#### ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

Государственное образовательное учреждение высшего профессионального образования

# «НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

## Д.А. Пестунов, В.В. Яковлев

# Реализация ШИМ на РІС-контроллерах

Методические рекомендации к выполнению лабораторной работы по курсу «Основы микропроцессорной техники» для студентов IV курса, обучающихся по направлениям 210100 «Электроника и наноэлектроника» и 201000 «Биотехнические системы и технологии»

Издательство

Томского политехнического университета

2010

УДК 681.325.5-181.48(076.5) ББК 32.973.26-04я73 П278

#### Пестунов Д.А.

П278 Реализация ШИМ на РІС-контроллерах: методические рекомендации к выполнению лабораторной работы по дисциплине «Основы микропроцессорной техники» для студентов, обучающихся по направлениям 210100 «Электроника и наноэлектроника» и 201000 «Биотехнические системы и технологии» / Пестунов Д.А., Яковлев В.В. — Национальный исследовательский Томский политехнический университет. — Томск: Изд-во Томского политехнического университета, 2010. — 16 с.

УДК 681.325.5-181.48(076.5) ББК 32.973.26-04я73

Методические указания рассмотрены и рекомендованы к изданию методическим семинаром кафедры Промышленной и медицинской электроники ИНК «25 » ноября 2010 г.

#### Рецензент

Кандидат технических наук, Заведующий лабораторией «Микропроцессорной техники» Пономарев С.В.

- © ГОУ ВПО «Национальный исследовательский Томский политехнический университет», 2010

- © Пестунов Д.А., Яковлев В.В., 2010

- © Оформление. Издательство Томского политехнического университета, 2010

# Реализация ШИМ на РІС-контроллерах

#### 1. Цель работы

Изучение основ работы модуля ССР (Capture, Compare, Modulation – Захват, Сравнение, Модуляция) в режиме ШИМ (Широтно-импульсная модуляция) в микроконтроллерах серии РІС16 и составлении программ. Получение практических навыков по работе с инструментально отладочными средствами отладки микропроцессорных систем.

#### 2. Введение

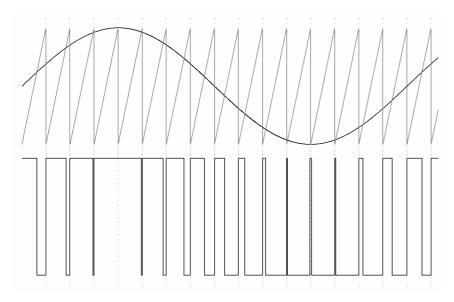

ШИМ (широтно-импульсная модуляция) представляет собой импульсный сигнал постоянной частоты и переменной скважности, т.е. отношения длительности импульса к периоду его следования. С помощью задания скважности можно менять среднее напряжение на выходе ШИМ, а постоянно меняя скважность – формировать сигнал любой формы, например синусоиду, как показано на рис. 1.

Рис. 1. Широтномодулированный сигнал можно получить, сравнивая сигнал требуемой формы с «пилой».

Основное достоинство импульсных регуляторов и стабилизаторов напряжения с ШИМ – высокий КПД работы, который достигается за счет работы силовых преобразователей в ключевом режиме. В данном случае силовой преобразователь (обычно в роли преобразователя выступает транзистор) работает не в режиме сопротивления, а в режиме ключей, т.е. транзистор либо полностью закрыт, при этом ток через него практически не течет, либо открыт так, что сопротивление его канала минимальное, и, В обоих случаях соответственно, минимальное падение напряжения. мощность значительно выделяемая ключе меньше мощности, передаваемой в нагрузку. Однако чтобы на нагрузку подавалось среднее

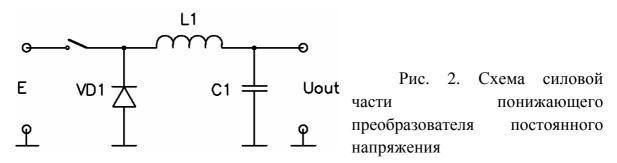

напряжение, импульсный сигнал сглаживается LC-фильтром (рис. 2), который рассчитывается с учетом частоты работы ШИМ, а также зависит от характера нагрузки.

Теперь остается сформировать управляющий сигнал для ключевых элементов. В большинстве устройств на долю ШИМ контроллера приходится не просто формирование последовательности импульсов определенной частоты, но и регулировка их скважности для поддержания определенного уровня выходного напряжения  $U_{out}$  (рис. 2) в зависимости от изменения входного напряжения E и нагрузки.

ТL494 — один из самых популярных ШИМ контроллеров, однако возможности его весьма ограниченны. Для построения многофункциональных источников питания или устройств, содержащих в себе импульсные преобразователи, обычно используют микроконтроллеры, в большинство из которых встроен модуль, реализующий ШИМ.

## 3. Модуль ССР в РІС контроллерах

Функцию широтно-импульсной модуляции в PIC-контроллерах легко реализовать, используя модуль ССР (Capture/Compare/PWM – Захват/Сравнение/ШИМ). В контроллерах серии PIC16F87х имеется два модуля ССР: ССР1 и ССР2, которые используют выводы порта PORTC: RC2/CCP1 и RC1/CCP2. Каждый модуль имеет в своем распоряжении по два 8-ми разрядных регистра CCPR1L(0x15)<sup>1</sup> и CCPR1H(0x16) для модуля ССР1 и CCPR2L(0x1b) и CCPR2H(0x1c) для модуля ССР2, которые могут использоваться в качестве:

16-разрядного регистра захвата данных; 16-разрядного регистра сравнения; двух 8-разрядных регистров ШИМ.

<sup>&</sup>lt;sup>1</sup> в скобках указаны адреса регистров в памяти данных. 0х15 – такая форма записи числа воспринимается компилятором MPLAB как шестнадцатиразрядное, то же самое, что и 15h

В регистрах CCP1CON(0x17) и CCP2CON(0x1D) находятся биты управления текущим режимом работы модулей ССР1 и ССР2, соответственно, а также два младших бита, задающих длительность импульса для режима ШИМ (см. табл. 1).

# <u>Таблица 1</u>

## Регистр **CCPxCON** (адреса 0x**17/0x1D**)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| -     | -   | CCPxX | CCPxY | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| Бит 7 |     |       |       |        |        |        | Бит 0  |

Обозначения: R – читаемый разряд; W – записываемый разряд; U - физически бит не существует, при обращении читается как 0; при включении контроллера или после его сброса все биты регистра сброшены в 0.

Назначение битов регистра состояния:

Биты 7-8: **Не используются** – читаются как «0»

Биты 5-4: **ССРхХ:ССРхУ** – младшие биты скважности ШИМ, восемь старших находится в регистре **ССРхL**.

Биты 3-0: **ССРхМ3:ССРхМ0** – Режим работы модуля ССРх

0000 = модуль ССРх выключен (сброс модуля ССРх)

0100 = захват по каждому заднему фронту сигнала

0101 = захват по каждому переднему фронту сигнала

0110 = захват по каждому 4-му переднему фронту сигнала

0111 = захват по каждому 16-му переднему фронту сигнала

1000 = сравнение, устанавливает выходной сигнал (устанавливается флаг CCPxIF в «1»)

1001 = сравнение, сбрасывает выходной сигнал (устанавливается флаг CCPxIF в «1»)

1010 = сравнение, на выходной сигнал не влияет (устанавливается флаг CCPxIF в «1»)

1011 = сравнение, триггер специальных функций (устанавливается флаг CCPxIF в «1», на вывод CCPx не влияет). CCP1 – сброс таймера TMR1. CCP2 – сброс таймера TMR1, запуск преобразования АЦП (если АЦП включено).

11хх = ШИМ режим.

В режим ШИМ оба модуля используют ресурсы таймера ТМR2, при этом в случае одновременной работы, оба ШИМ будут иметь одинаковые частоту и фазу. Работа модулей ССР1 и ССР2 идентична, за исключением функционирования, так называемого триггера специального события (дополнительную информацию по работе модулей ССР PIC16F87x смотрите в технической документации DS30292C Microchip Technology Incorporated,

USA). В ШИМ режиме модуль ССР1 использует вывод RC2/CCP1 в качестве выхода генерации ШИМ, а модуль ССР2 – RC1/CCP2. Далее будет описана работа модуля ССР1 в режиме ШИМ, модуль ССР2 работает аналогично.

Вывод RC2 нужно настроить на выход сбросом соответствующего бита в регистре направления TRISC.

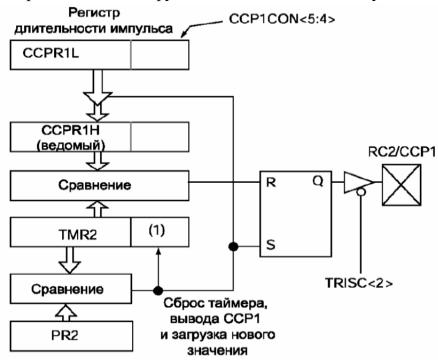

На рис. 3 показана функциональная схема модуля ССР1 в режиме ШИМ.

Рис. 3. Структурная схема модуля ССР1 в режиме ШИМ.

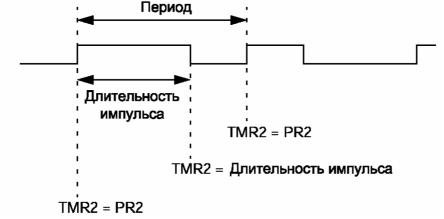

На рис. 4 показана временная диаграмма одного цикла ШИМ. Период ШИМ определяется настройками таймера TMR2 и содержимым регистра PR2 и может быть вычислен по формуле

Период ШИМ = [(PR2)+1]\*4  $T_{OSC}*$ коэффициент предделителя TMR2. Частота ШИМ = 1/период ШИМ.

Рис. 4. Временная диаграмма одного цикла ШИМ

Когда TMR2 сравнивается с PR2, выполняются следующие действия:

- TMR2 сбрасывается в '0';

- Устанавливается высокий уровень сигнала на выходе ССР1 (если длительность импульса нулевая, то высокий уровень устанавливаться не будет);

- Модуль ШИМ начинает новый цикл, загружая значение из регистра CCPR1L в CCPR1H.

*Примечание!* Выходной делитель TMR2 не влияет на частоту ШИМ. Он может использоваться для отсчета времени, когда необходимо изменить скважность ШИМ.

Скважность ШИМ определяется значениями регистра CCPR1L и двух битов CCP1CON<5:4>, причем старшие 8 бит сохраняются в CCPR1L. Для вычисления длительности сигнала высокого уровня применяется формула:

Длительность импульса ШИМ = (CCPR1L:CCP1CON<5:4>) \*  $4T_{OSC}$  \* коэффициент предделителя TMR2.

Значение CCPR1L:CCP1CON<5:4> может быть изменено в любое время, но значение в регистре CCPR1H не изменится пока не произойдет соответствие TMR2 и PR2. Регистр CCPR1H и внутренняя 2-разрядная защелка образуют буфер ШИМ, который необходим при записи нового значения длительности импульса ШИМ, поэтому в этом режиме регистр CCPR1H программно не доступен для записи.

Когда значение CCPR1 и внутренней 2-разрядной защелки совпадет по значению TMR2 и внутреннему 2-разрядному счетчику, вывод RC2/CCP1 будет сброшен в '0'.

**Примечание!** Если длительность импульса ШИМ больше периода ШИМ, вывод ССР1 не будет иметь низкий уровень сигнала.

Рекомендуемая последовательность настройки модуля ССР в ШИМ режиме:

- 1. Установить период ШИМ в регистре PR2;

- 2. Установить длительность импульса в регистрах CCPR1L и CCP1CON <5:4>;

- 3. Настроить вывод ССР1 как выход, сбросив бит TRISC<2>;

- 4. Настроить предделитель и включить TMR2 в регистре T2CON;

- 5. Включить ССР1 в режиме ШИМ.

В таблице 2 приведен регистр управления таймером 2.

Таблица 2

Регистр **T2CON**: регистр управления таймера 2 (адрес 0x12)

U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

- TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0

Бит 7

Обозначения: R — читаемый разряд; W — записываемый разряд; U - физически бит не существует, при обращении читается как 0; при включении контроллера или после его сброса все биты регистра сброшены в 0.

Назначение битов регистра T2CON приведено ниже.

Биты 6-3: **TOUTPS3:TOUTPS0** – коэффициент деления постделителя

0000 = 1:1

0001 = 1:2

0010 = 1:3

1111 = 1:16

Бит 2: **TMR2ON** – управление таймером 2

1 = таймер2 включен

0 = таймер2 выключен

Биты 1-0: **T2CKPS1:T2CKPS0** – коэффициент деления предделителя

00 = 1:1

01 = 1:4

1x = 1:16

## 4. Оборудование

- Компьютер IBM PC/AT с установленным ПО MPLAB IDE.

- Программатор-отладчик MPLAB ICD-I.

- Демонстрационная плата MPLAB-ICD с установленным микроконтроллером PIC16F877.

- Источник питания 9В, 0.2 А.

### 5. Пример использования модуля ССР

LIST P=16f877, R=DEC

**ERRORLEVEL** 0, -302

INCLUDE <p16f877.inc>

STACK\_W EQU 0x71

STACK\_STATUS EQU 0x72

```

;Директивой EQU можно присвоить любой ячейке памяти

;данных уникальное имя (ячейку с адресом 0х71

;назвали STACK_W)

; А почему здесь не использовать ячейку с адресом

;0x70, 0x20 или 0x21? Какой еще директивой можно

;присвоить имя?

ORG

0x0

NOP

MY_RESET CLRF INTCON

GOTO BEGIN

ORG

0x4

;Директива ORG указывает компилятору на адрес в па-

;мяти, с которого будет располагаться программа, на-

;писанная под ней.

;В данном случае с адреса 4! Вам он о чем-нибудь

;говорит?

MOVWF

STACK W

MOVF STATUS, W

MOVWF STACK STATUS

BCF

STATUS, RPO

BCF

STATUS, RP1

; Сохранили содержимое аккумулятора и регистра STATUS

;в памяти данных - т.е. как бы создали свой

;искусственный стек

. . .

. . .

;здесь Вы можете поместить подпрограмму обработки

;прерываний

STACK_STATUS,W

INT_RETURN MOVF

MOVWF

STATUS

MOVF

STACK W, W

RETFIE

;После вытаскиваем из стека STATUS и аккумулятор и

;возвращаемся в основную программу

BEGIN

;В начале любой программы производим инициализацию

;периферии: портов и модулей контроллера

BANKSEL

TRISB

;BANKSEL - это директива выбора банка, в котором

```

```

;находится приведенный регистр. А как переключиться

;между банками иначе? Все ли здесь правильно?

MOVLW

0xFF

MOVWF

PR2

CLRF

TRISC

CLRF

ADCON1

;Порт С настроили на вывод. А как настроили АЦП?

BCF

STATUS, RPO ; BANKO

CLRF

CCPR1L

BCF

CCP1CON, 5

BCF

CCP1CON, 4

MOVLW B'00000100'

MOVWF T2CON

MOVLW B'00001111'

MOVWF CCP1CON

;Настроили модули таймера ТMR2 и ССР1. Как настроили

;- см. справочник

MOVLW B'10010001'

MOVWF ADCON0

;Еще поработали с модулем АЦП.

; Может необходимо еще что-нибудь настроить?

; BASIC_PROGRAM_LOOP____

;Когда все настроено, можно с ними работать.

;Попробуйте разобраться, что делают эти 6 строчек

;программы:)

BASIC_PROGRAM_LOOP

BSF

ADCON0, GO

WAIT_ADC

BTFSC ADCON0,GO

WAIT ADC

GOTO

ADRESH, W

MOVF

MOVWF CCPR1L

BASIC PROGRAM LOOP

GOTO

;Попробуйте написать программу, которая выполняет

; эту задачу, не используя ресурсы модуля ССР

END

```

#### 6. Варианты заданий

- 1. При сбросе контроллера яркость светодиода HL1 (см. схему прил. 3) плавно нарастает.

- 2. По нажатию кнопки 'RB0' яркость светодиода HL2 плавно нарастает, а при отпускании гаснет, но в 2 раза быстрее.

- 3. Свечение светодиода HL2 плавно меняется от максимальной до минимальной яркости и наоборот. По нажатию кнопки 'RB0' яркость диода фиксируется.

- 4. По нажатию кнопки 'RB0' яркость светодиод HL1 плавно нарастает, а яркость светодиода HL2 спадает.

- 5. Яркость светодиода HL2 меняется в зависимости от положения движка переменного резистора.

- 6. Яркость светодиодов HL1 и HL2 меняются в зависимости от положения движка переменного резистора, причем обратно пропорционально друг другу.

- 7. По нажатию кнопки 'RB0' яркость светодиода HL1 устанавливается согласно входному напряжению на входе RA0/ANO, а при отпускании гаснет.

- 8. По нажатию кнопки 'RB0' яркости светодиодов HL1 и HL2 плавно достигают значения соответствующего входному напряжению на входе RA0/AN0, причем светодиод HL1 с уровня минимальной яркости, HL2 максимальной.

## 7. Контрольные вопросы

- 1. Какой период ШИМ задан программой, показанной в примере?

- 2. Чем определяется период ШИМ?

- 3. Какой минимальный коэффициент заполнения ШИМ обеспечивает модуль ССР контроллера?

- 4. Чем определяется длительность импульса?

- 5. Возможна ли работа с модулем ССР по прерываниям?

- 6. Возможна ли работа обоих модулей ССР1 и ССР2 в режиме ШИМ?

- 7. Какую минимальную скважность ШИМ (>1) обеспечивает модуль ССР контроллера?

- 8. С какими регистрами работают модули ССР1 и ССР2?

- 9. Какими могут быть периоды ШИМ, если  $F_{OSC}$ =5М $\Gamma$ ц?

# Приложение 1

Карта памяти данных контроллера PIC16F877

| Банк 0         |            | Банк 1                        |            | Банк 2                        |              | Банк 3                        |              |

|----------------|------------|-------------------------------|------------|-------------------------------|--------------|-------------------------------|--------------|

| Регистр        |            |                               | Адрес      | Регистр Адрес                 |              | Регистр                       | Адрес        |

| INDF           | 00h        | INDF                          | 80h        | INDF                          | 100h         | INDF                          | 180h         |

| TMR0           | 01h        | OPTION_REG                    | 81h        | TMR0                          | 101h         | OPTION_REG                    | 181h         |

| PCL            | 02h        | PCL                           | 82h        | PCL                           | 102h         | PCL                           | 182h         |

| STATUS         | 03h        | <b>STATUS</b>                 | 83h        | STATUS                        | 103h         | STATUS                        | 183h         |

| FSR            | 04h        | FSR                           | 84h        | FSR                           | 104h         | FSR                           | 184h         |

| PORTA          | 05h        | TRISA                         | 85h        | -                             | 105h         | -                             | 185h         |

| PORTB          | 06h        | TRISB                         | 86h        | PORTB                         | 106h         | TRIBSB                        | 186h         |

| PORTC          | 07h        | TRISC                         | 87h        | -                             | 107h         | -                             | 187h         |

| PORTD          | 08h        | TRISD                         | 88h        | -                             | 108h         | -                             | 188h         |

| PORTE          | 09h        | TIRSE                         | 89h        | -                             | 109h         | -                             | 189h         |

| PCLATH         | 0Ah        | PCLATH                        | 8Ah        | PCLATH                        | 10Ah         | PCLATH                        | 18Ah         |

| INTCON         | 0Bh        | INTCON                        | 8Bh        | INTCON                        | 10Bh         | INTCON                        | 18Bh         |

| PIR1<br>PIR2   | 0Ch<br>0Dh | PIE1<br>PIE2                  | 8Ch        | EEDATA<br>EEADR               | 10Ch<br>10Dh | EECON1<br>EECON2              | 18Ch         |

| TMR1L          |            | PIE2<br>PCON                  | 8Dh        |                               |              | EECON2                        | 18Dh         |

| TMR1L<br>TMR1H | 0Eh<br>0Fh | FCON                          | 8Eh<br>8Fh | EEDATH<br>EEADRH              | 10Eh<br>10Fh | -                             | 18Eh<br>18Fh |

| T1CON          | 10h        | <u>-</u>                      | 90h        | EEADKH                        | 110h         | -                             | 190h         |

| TMR2           | 11h        | SSPCON2                       | 91h        |                               | 11011        |                               | 19011        |

| T2CON          | 12h        | PR2                           | 92h        |                               |              |                               |              |

| SSBUF          | 13h        | SSPADD                        | 93h        |                               |              |                               |              |

| SSPCON         | 14h        | SSPSTAT                       | 94h        |                               |              |                               |              |

| CCPR1L         | 15h        | -                             | 95h        |                               |              |                               |              |

| CCPR1H         | 16h        | -                             | 96h        |                               |              |                               |              |

| CCP1CON        | 17h        | -                             | 97h        | Регистры                      |              | Регистры                      |              |

| RCSTA          | 18h        | TXSTA                         | 98h        | общего                        |              | общего                        |              |

| TXREG          | 19h        | <b>SPBRG</b>                  | 99h        | назначения                    |              | назначения                    |              |

| RCREG          | 1Ah        | -                             | 9Ah        | (16 байт)                     |              | (16 байт)                     |              |

| CCPR2L         | 1Bh        | -                             | 9Bh        |                               |              |                               |              |

| CCPR2H         | 1Ch        | -                             | 9Ch        |                               |              |                               |              |

| CCP2CON        | 1Dh        | <u> </u>                      | 9Dh        |                               |              |                               |              |

| ADRESH         | 1Eh        | ADRESL                        | 9Eh        |                               |              |                               |              |

| ADCON0         | 1Fh        | ADCON1                        | 9Fh        |                               | 11Fh         |                               | 19Fh         |

|                | 20h        |                               | 0A0h       |                               | 0A0h         |                               | 0A0h         |

|                |            | Регистры                      |            | Регистры                      |              | Регистры                      |              |

|                |            | общего                        |            | общего                        |              | общего                        |              |

| D              |            | назначения                    |            | назначения                    |              | назначения                    |              |

| Регистры       |            | (80 байт)                     |            | (80 байт)                     |              | (80 байт)                     |              |

| общего         |            |                               | 0EFh       |                               | 16Fh         |                               | 1EFh         |

| назначения     |            |                               |            |                               |              |                               |              |

| (96 байт)      |            | Ofnoverse                     | 0F0h       | Ognovica                      | 170h         | Ofmary                        | 1F0h         |

|                |            | Обращение к                   |            | Обращение к                   |              | Обращение к                   |              |

|                |            | регистрам 70h-<br>7Fh банка 0 |            | регистрам 70h-<br>7Fh банка 0 |              | регистрам 70h-<br>7Fh банка 0 |              |

|                | 7Fh        | /1711 Uahka U                 | 0FFh       | /111 Uahka U                  | 17Fh         | /1711 Uahka U                 | 1FFh         |

|                | / 1 11     |                               | OLTH       |                               | 1/1/11       |                               | 11.1,11      |

# Приложение 2

## Система команд РІС16F877

|     |                                              | Система команд г тетогот                 | TT            |      |       |

|-----|----------------------------------------------|------------------------------------------|---------------|------|-------|

| №   | Мнемокод                                     | Описание                                 | Изм.<br>флаги | Цикл | Прим. |

|     |                                              |                                          | C, DC,        |      |       |

| 1.  | ADDWF f,d                                    | Сложение W c f                           | Z             | 1    | 1,2   |

| 2.  | ANDWF f,d                                    | Логическое И W и f                       |               | 1    | 1,2   |

| 3.  | CLRF f                                       | Сброс регистра f                         | Z             | 1    | 2     |

| 4.  | CLRW                                         | Сброс регистра W                         | Z             | 1    |       |

| 5.  | COMF f,d                                     | Инверсия регистра f                      | Z             | 1    | 1,2   |

| 6.  | DECF f,d                                     | Декремент регистра f                     | Z             | 1    | 1,2   |

|     |                                              | Декремент f и пропуск следующей          |               |      |       |

| 7.  | DECFSZ f,d                                   | команды, если результат декремента       | _             | 1(2) | 1,2,3 |

| -   |                                              | равен 0                                  |               |      |       |

| 8.  | INCF f,d                                     | Инкремент регистра f                     | Z             | 1    | 1,2   |

|     |                                              | Инкремент f и пропуск следующей          |               |      | 1,2,3 |

| 9.  | INCFSZ f,d                                   | команды, если результат декремента       | _             | 1(2) |       |

|     |                                              | равен 0                                  |               |      |       |

| 10. | IORWF f,d                                    | Логическое ИЛИ W и f                     | Z             | 1    | 1,2   |

| 11. | MOVF f,d                                     | Пересылка регистра f                     | Z             | 1    | 1,2   |

| 12. | MOVWF f                                      | Пересылка W в f                          |               | 1    |       |

| 13. | NOP                                          | Холостая команда                         | —             | 1    |       |

| 14. | RLF f,d                                      | Сдвиг f влево через перенос              | C             | 1    | 1,2   |

| 15. | RRF f,d                                      | Сдвиг f вправо через перенос             | C             | 1    | 1,2   |

| 16. | SUBWF f,d                                    | Вычитание W из f                         | C, DC,<br>Z   | 1    | 1,2   |

| 17. | SWAPF f,d                                    | Обмен местами тетрад в f                 | _             | 1    | 1,2   |

| 18. | XORWF f,d                                    | Исключающее ИЛИ W и f                    | Z             | 1    | 1,2   |

| 19. | BCF f,b                                      | <b>BCF f,b</b> Сброс бита b в регистре f |               | 1    | 1,2   |

| 20. | <b>BSF f,b</b> Установка бита b в регистре f |                                          | _             | 1    | 1,2   |

| 21. | BTFSC f,b                                    | Пропустить следующую команду, если       |               | 1(2) | 3     |

| 21. | DIFSC 1,0                                    | бит b, в регистре f равен нулю           |               |      |       |

| 22. | BTFSS f,b                                    | Пропустить следующую команду, если       | _             | 1(2) | 3     |

|     |                                              | бит b, в регистре f равен единице        |               |      |       |

| 23. | ADDLW k                                      | Сложение константы с W.                  | C, DC,Z       | 1    |       |

| 24. | ANDLW k                                      | Логическое И константы и W               | Z             | 1    |       |

| 25. | CALL k                                       | Вызов подпрограммы                       | —<br>—        | 2    |       |

| 26. | CLRWDT                                       | Сброс сторожевого таймера (WDT)          | TO,PD         | 1    |       |

| 27. | GOTO k                                       | Переход по адресу к                      | _             | 2    |       |

| 28. | IORLW k                                      | Логическое ИЛИ константы и W             | Z             | 1    |       |

| 29. | MOVLW k                                      | Пересылка константы в W                  | _             | 1    |       |

| 30. | RETFIE                                       | Возврат из прерывания.                   |               | 2    |       |

| 31. | RETLW k                                      | Возврат из подпрограммы с загрузкой      |               | 2    |       |

|     |                                              | константы в W                            |               |      |       |

| 32. |                                              | RETURN Возврат из подпрограммы.          |               | 2    |       |

| 33. | SLEEP                                        | Переход в режим SLEEP                    | TO,PD         | 1    |       |

| 34. | SUBLW k                                      | Вычитание W из константы.                | C, DC,Z       | 1    |       |

| 35. | XORLW k                                      | Исключающее ИЛИ константы и W            | Z             | 1    |       |

Описание полей кода операции

| Символ | Описание                                                                                       |  |  |  |

|--------|------------------------------------------------------------------------------------------------|--|--|--|

| f      | Адрес регистра (0х00-0х7F) – файл                                                              |  |  |  |

| W      | Рабочий регистр                                                                                |  |  |  |

| b      | Номер бита в 8-ми разрядном регистре                                                           |  |  |  |

| k      | Константа                                                                                      |  |  |  |

| d      | Регистр назначения: d=0 - результат в регистре W d=1 - результат в регистре f По умолчанию d=1 |  |  |  |

#### Примечания:

- 1. Когда модифицируется регистр порта ввода/вывода, (например MOVF PORTB,1), значение считывается непосредственно с ножек микросхемы. Например, если в регистре порта «1», а контакты конфигурированы как входы и внешнее устройство установит низкий уровень, то в регистр данных будут записаны «0».

- 2. Если команда выполняется над регистром TMR0 (когда d=1, результат записывается в регистр таймера 0), то предделитель, будет обнулен.

- 3. Если счетчик программ (PC) изменяется или результат проверки условия истинен, то команда выполняется за два цикла. Во втором цикле выполняется команда NOP.

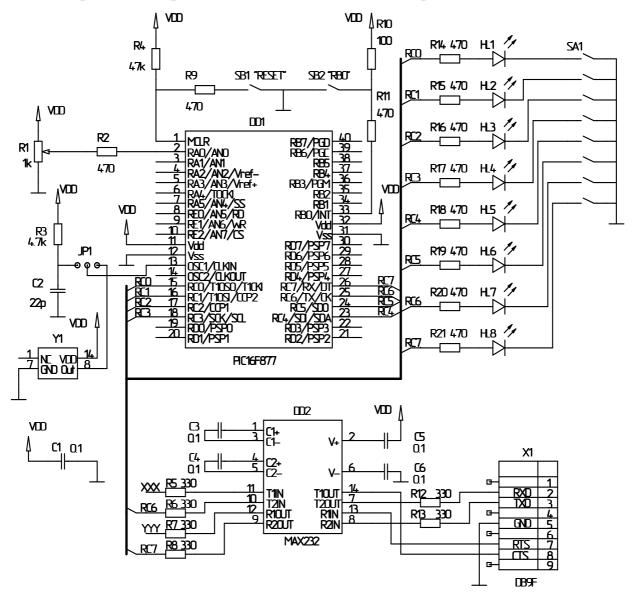

Приложение 3

Фрагменты принципиальной схемы демонстрационной платы

#### Учебное издание

# Пестунов Дмитрий Александрович Яковлев Владислав Викторович

# Реализация ШИМ на РІС-контроллерах

Методические рекомендации к выполнению лабораторной работы по курсу «Основы микропроцессорной техники» для студентов IV курса, обучающихся по направлениям 210100 «Электроника и наноэлектроника» и 201000 «Биотехнические системы и технологии»

Отпечатано в Издательстве ТПУ в полном соответствии с качеством предоставленного оригинал-макета

Подписано к печати 25.11.2010. Формат 60х84/16. Бумага «Снегурочка». Печать XEROX. Усл.печ.л. 0,93. Уч.-изд.л. 0,84. Заказ . Тираж 100 экз.

Национальный исследовательский Томский политехнический университет

Система менеджмента качества

Томского политехнического университета сертифицирована

NATIONAL QUALITY ASSURANCE по стандарту ISO 9001:2008

**ИЗДАТЕЛЬСТВО** ТПУ. 634050, г. Томск, пр. Ленина, 30 Тел./факс: 8(3822)56-35-35, www.tpu.ru