# Общие требования к выполнению лабораторных работ по программированию

# Программа работы

- 1. Работа выполняется с использованием программы Visual Studio (лицензия ТПУ) и NotePad или NotePad++ (бесплатная лицензия). Вместо NotePad и NotePad++ можно использовать стандартный Блокнот ОС Windows.

- 2. Пишется исходный код в указанной в работе программе. Для случая работ в Visual Studio студент самостоятельно компилирует файл. На проверку, помимо отчета с описанием работы созданного приложения, присылается ехе-файл. Для случая написания кода для микроконтроллера, студентом предоставляется только текстовый файл с исходным кодом. Компиляция и программирование микроконтроллера осуществляется преподавателем.

- 3. Все лабораторные проекты будут выполняться на микроконтроллере STM32F429IIT6.

# Требования к отчёту по работе

Отчет по лабораторной работе должен содержать:

- 1. Титульный лист.

- 2. Цель работы.

- 3. Этапы выполнения работы.

- 4. Результаты исследований в виде таблиц и графиков с пояснениями к ним.

- 5. Выводы по работе, в которых должен содержаться детальный анализ полученных результатов и их интерпретация.

# Лабораторная работа № 4. Разработка программы контроллера: управление периферией, обмен данными, таймеры.

## Изучение системы тактирования микроконтроллера

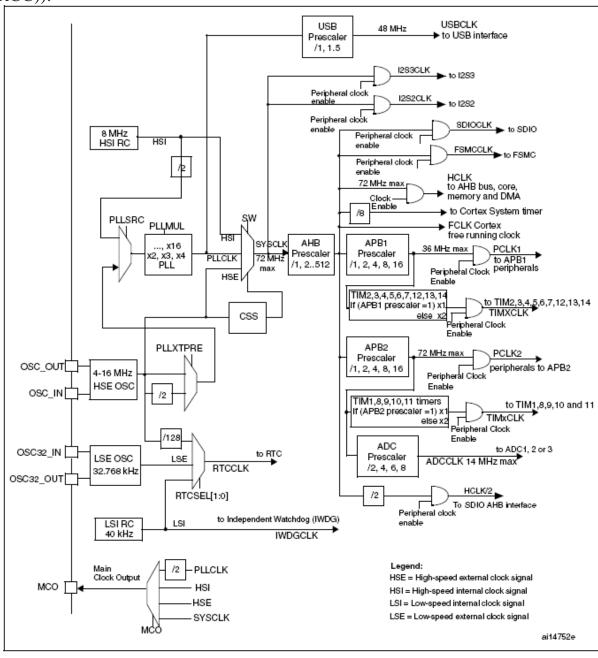

Ниже представлена структурная схема системы формирования тактовых частот, из документации на микроконтроллер (раздел reset and clock control (RCC)).

Как можно увидеть из данной схемы, практически все блоки микроконтроллера тактируются от линии **SYSCLK**, что расшифровывается как System Clock (системная тактовая частота).

Как следует из документации и схемы, источниками для системной тактовой частоты могут служить 3 генератора:

- Генератор HSI внутренний высокоскоростной.

- Генератор HSE внешний высокоскоростной.

- Внутренний PLL система фазовой автоподстройки частоты (ФАПЧ)). В нашем случае можно сказать, что это умножитель частоты с управляемым коэффициентом умножения.

На самом деле более правильно сказать, что источниками могут быть только HSI и HSE, частота которых может умножаться, а может и нет. Разберемся с ними поподробнее.

Встроенный RC генератор (HSI). Встроенный в микропроцессор генератор HSI вырабатывает тактовую частоту, например, 8 МГц. Генератор автоматически запускается при появлении питания *Vcc* и при выходе в нормальный режим работы выставляет флаг **HSIRDY** в регистре **RCC\_CR**. Первоначально процессорное ядро запускается на тактовой частоте HSI. К преимуществам относится быстрое время начала генерации тактовой частоты после подачи питания и отсутствие необходимости в использовании дополнительных электронных компонентов для работы микроконтроллера.

Недостаток – низкая стабильность частоты генерируемого сигнала, а при умножении на PLL погрешность тоже умножается. Например, если частота HSI при разных температурных условиях плавает от 7.3 до 8.7МГц. При множителе PLL в 9 на выходе будет разброс уже от 65.7 до 78.3 МГц.

Генератор HSI может быть включен/выключен управлением бита **HSION** регистра **RCC\_CR**.

**Внешний генератор (HSE).** В качестве внешнего генератора могут выступать:

- Внешний тактовый сигнал с частотой не выше 25МГц, поданный на ножку **OSC\_IN** в то время, как нога **OSC\_OUT** находится в высокоимпендансном состоянии.

- Внешний кварцевый резонатор подключенный на ножки **OSC\_IN** и **OSC\_OUT**. Внешний кварцевый резонатор должен быть в диапазоне от 4 до 25МГц и при его использовании достигается очень высокая стабильность частоты работы генератора.

Внешний генератор HSE по умолчанию выключен и его включение/выключение управляется битом **HSEON** регистра **RCC\_CR**. После включения HSE и его выхода в рабочий режим устанавливается бит **HSERDY** кроме этого, может быть сгенерировано прерывание. Также как и сигнал с генератора HSI, сигнал HSE может быть подан напрямую в качестве системного тактового сигнала либо поступать в блок умножения. Но в отличие от HSI в блок умножения он может поступать напрямую, либо пройдя через делитель на 2.

**PLL.** Внутренний умножитель частоты может умножать вошедший тактовый сигнал с одного из трех источников (HSI/2; HSE; HSE/2) на множитель от 2-х до 16-ти. По умолчанию умножитель выключен и его включение/выключение управляется битом **PLLON** регистра **RCC\_CR**. После включения PLL и его выхода в рабочий режим устанавливается бит **PLLRDY** кроме этого, может быть сгенерировано прерывание.

Работа умножителя конфигурируется через регистр **RCC\_CFGR**.

Все манипуляции над его режимами работы должны проводиться только при выключенном PLL.

В данном регистре (смотри документацию к МК):

- Бит PLLSRC задает источник умножения, либо HSI либо HSE.

- Бит **PLLXTPRE** задает будет ли сигнал с HSE предварительно делиться на 2 или нет.

- Биты **PLLMUL[3:0**] задают коэффициент умножения от 2-х до 16-ти.

Дальше системная тактовая частота попадает в делитель шины АНВ, который делит ее на делитель от 1 до 512, и все остальные блоки получают на вход уже эту деленную частоту (некоторые блоки имеют еще дополнительные делители). По схеме все видно, какой блок имеет делитель, а какой нет, какие коэффициенты деления у делителей, и какая периферия в итоге какую частоту получает.

Так же на схеме подписаны максимальные допустимые частоты для блоков. Все делители имеющие управляемые коэффициенты могут быть настроены, что в целом позволяет довольно гибко варьировать частоты отдельных блоков в различных пределах. Кроме того, на схеме это не показано, очень важно знать и помнить 2 вещи:

- 1. Какие блоки к какой шине подключены. Например, порты ввода вывода подключены к шине APB2, контроллеры шины I2C к шине APB1, контроллера прямого доступа к памяти на шине AHB а, например, таймеры, частью подключены к APB2, а частью на APB1.

- 2. Каждый блок имеет свой вход тактовых сигналов и бит управления этим входом. И по умолчанию практически все блоки отключены от тактовых сигналов!

Т.е., если нужна работа какого-то блока: GPIO, DMA, ADC, DAC, таймеров и т.д., то не необходимо подавать на них тактовые сигналы, т.е. устанавливать соответствующие биты! Иначе работать ничего не будет!

### Пример программного кода

```

1 ___IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* Конфигурацяи SYSCLK, HCLK, PCLK2 и PCLK1 */

/* Включаем HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* Ждем пока HSE не выставит бит готовности либо не выйдет таймаут*/

```

```

9

do

10

{

11

HSEStatus = RCC->CR & RCC CR HSERDY;

12

StartUpCounter++;

13

}

14

while( (HSEStatus == 0) && (StartUpCounter != HSEStartUp TimeOut));

15

16

if ( (RCC->CR & RCC CR HSERDY) != RESET)

17

18

HSEStatus = (uint32 t)0x01;

19

20

21

else

22

23

HSEStatus = (uint32_t)0x00;

24

}

25

26

/* Если HSE запустился нормально */

27

if ( HSEStatus == (uint32_t)0x01)

28

29

/* Включаем буфер предвыборки FLASH */

30

FLASH->ACR |= FLASH ACR PRFTBE;

31

32

/* Конфигурируем Flash на 2 цикла ожидания */

33

/* Это нужно потому, что Flash не может работать на высокой частоте

34

*/

35

36

37

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH ACR LATENCY);

38

FLASH->ACR |= (uint32_t)FLASH ACR LATENCY 2;

39

40

41

/* HCLK = SYSCLK */

42

RCC->CFGR |= (uint32_t)RCC CFGR HPRE DIV1;

43

44

/* PCLK2 = HCLK */

45

RCC->CFGR |= (uint32_t)RCC CFGR PPRE2 DIV1;

46

47

/* PCLK1 = HCLK */

48

RCC->CFGR |= (uint32_t)RCC CFGR PPRE1 DIV2;

49

50

/* Конфигурируем множитель PLL configuration: PLLCLK = HSE * 9 = 72 MHz

51

52

53

/* При условии, что кварц на 8МГц! */

54

/* RCC_CFGR_PLLMULL9 - множитель на 9. Если нужна другая частота,

55

не 72МГц */

56

/* то выбираем другой множитель. */

57

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC CFGR PLLSRC |

58

RCC CFGR PLLXTPRE | RCC CFGR PLLMULL));

59

RCC->CFGR |= (uint32_t)(RCC CFGR PLLSRC HSE | RCC CFGR PLLMULL9);

60

61

/* Включаем PLL */

62

RCC->CR |= RCC CR PLLON;

63

64

/* Ожидаем, пока PLL выставит бит готовности */

65

66

while((RCC->CR & RCC CR PLLRDY) == 0)

67

68

// Ждем

69

}

70

```

```

71

/* Выбираем PLL как источник системной частоты */

72

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC CFGR SW));

73

RCC->CFGR |= (uint32_t)RCC CFGR SW PLL;

74

75

/* Ожидаем, пока PLL выберется как источник системной частоты */

76

while ((RCC->CFGR & (uint32_t)RCC CFGR SWS) != (uint32_t)0x08)

77

78

// Ждем

else

/* Не работает */

}

```

# Настройка базового таймера

Таймеры — это периферия контроллера STM32, позволяющая отсчитывать интервалы времени. Следует начать с того, что в контроллерах STM32 существуют таймеры, которые делятся на три группы. Самые простые это *Basic timers*. Они хороши тем, что очень просто настраиваются и управляются при помощи минимума регистров. Все что они умеют это отсчитывать временные интервалы и генерировать прерывания, когда таймер досчитает до заданного значения. Следующая группа (*general-purpose timers*) более продвинутая — они умеют генерировать ШИМ, умеют считать импульсы, поступающие на определённые ножки и т.д. И самый мощный таймер — это *advanced-control timer*.

Basic таймеры (TIM6 и TIM7) подключены к шине APB1. Основной регистра –  $TIMx_CNT$  (здесь и далее x — номер basic таймера 6 или 7). Это счётный 16-ти битный регистр, занимающийся непосредственно счётом времени. Каждый раз, когда с шины APB1 приходит тактовый импульс, содержимое этого регистра увеличивается на единицу. Когда регистр переполняется, все начинается с нуля. У таймера есть предделитель, управлять которым можно при помощи регистра TIMx\_PSC. Записав в него значение, например, 24000-1 (при частоте шины АРВ1 24 МГц) мы заставим счётный регистр TIMx\_CNT увеличивать свое значение каждую (Частоту **APB1** делим на число в регистре предделителе и получаем сколько раз в секунду увеличивается счётчик). Единицу нужно вычесть потому, что если в регистре ноль, то это означает, что включен делитель на единицу. Для того чтоб счётчик обнулялся досрочно, а не когда досчитает до предельного значения 0xFFFF, служит регистр **TIMx\_ARR**. Записываем в него то число, до которого должен досчитывать регистр **TIMx\_CNT** перед тем как обнулиться. Если мы хотим, чтобы прерывание возникало раз в секунду, то нам нужно записать туда 1000. Для включения таймера установливаем бит СЕМ в

регистре **TIMx\_CR1**. Этот бит разрешает начать отсчёт, соответственно если его сбросить, то отсчет остановится. В регистре **TIMx\_DIER**. Интересен бит **UIE**, который активирует возможность прерывания программы микроконтроллера.

#### Пример программного кода

```

//-----Base timer TIM6 -> APB1

#define

TIM6 ON

(1 << 4)

#define

TIM6 RESET FLAG

(0x1)

#define

((1 << 7) | (1 << 3) | (1 << 2) | (1 << 1)

TIM6_CR1_CLEAR

|(0x1)\rangle

#define

((1 << 6) | (1 << 5) | (1 << 4))

TIM6 CR2 CLEAR

TIM6_DIER_CLEAR ((1 << 8) | (0x1))

#define

RCC->APB1ENR |= TIM6 ON; // activate TIM6 - it is on APB1 port

TIM6->CR2 &= ~TIM6 CR2 CLEAR;

// Bits 6:4 MMS[2:0]: Master mode

selection: 000: Reset - the UG bit from the TIMx_EGR register is

used as a trigger output (TRGO).

TIM6->DIER &= ~TIM6 DIER CLEAR;

TIM6->DIER |= 0x00000001; // UIE: Update interrupt enable: 1: Update

interrupt enabled - allow to interrupt program when timer reached max

(set up in ARR).

TIM6->SR = ~TIM6 RESET FLAG; // UIF: Update interrupt. This bit is

set by hardware on an update event. It is cleared by software. 0

= reset flag

TIM6->PSC = 0x20CF;

// prescaller: fCK PSC / (PSC[15:0] + 1),

fCK_PSC = F_APB1 (42 MHz)* 2 (see Init_RCC function, in default

it was 16 MHz): 1/0.1 ms = 10 kHz = 84 MHz/(8399 + 1)

// number of cycles of rescaller: time =

TIM6->ARR = 0x3E7;

TIM6->PSC * TIM6->ARR: 0.1 s = 0.1ms * (1000 - 1)

TIM6->CR1 &= ~TIM6 CR1 CLEAR;

TIM6->CR1 |= (1 << 7) |

// ARPE: Auto-reload preload enable: 1:

TIMx ARR register is buffered.

(1 << 2)

// URS: Update request source: 0 - any

sourse of update, 1- Only counter overflow/underflow generates an

update interrupt or DMA request if enabled.

(0x00000001);

// CEN: 1: Counter enabled

```

# Настройка портов ввода-вывода

За включение тактирования периферийных блоков отвечают регистры RCC XXX peripheral clock enable register. На месте XXX могут стоять шины AHB1, AHB2, AHB3, APB1 и APB2. Например, тактирование периферийного блока GPIOD включается установкой «1» в третий бит регистра RCC AHB1 peripheral clock enable register (RCC AHB1ENR).

#### 7.3.10 RCC AHB1 peripheral clock enable register (RCC\_AHB1ENR)

Address offset: 0x30

Reset value: 0x0010 0000

Access: no wait state, word, half-word and byte access.

| 31            | 30                      | 29          | 28                  | 27                 | 26                 | 25           | 24       | 23          | 22          | 21          | 20               | 19          | 18            | 17          | 16          |

|---------------|-------------------------|-------------|---------------------|--------------------|--------------------|--------------|----------|-------------|-------------|-------------|------------------|-------------|---------------|-------------|-------------|

| Reser-<br>ved | OTGH<br>S<br>ULPIE<br>N | OTGH<br>SEN | ETHM<br>ACPTP<br>EN | ETHM<br>ACRXE<br>N | ETHM<br>ACTXE<br>N | ETHMA<br>CEN | Reserved |             | DMA2E<br>N  | DMA1E<br>N  | CCMDAT<br>ARAMEN | Res.        | BKPSR<br>AMEN | Rese        | erved       |

|               | rw                      | rw          | rw                  | rw                 | rw                 | rw           |          |             | rw          | rw          |                  |             | rw            | w           |             |

| 15            | 14                      | 13          | 12                  | 11                 | 10                 | 9            | 8 7      |             | 6           | 5           | 4                | 3           | 2             | 1           | 0           |

|               | Reserved                |             | CRCE<br>N           |                    |                    | GPIOI<br>N   |          | GPIOH<br>EN | GPIOG<br>EN | GPIOFE<br>N | GPIOEEN          | GPIOD<br>EN | GPIOC<br>EN   | GPIO<br>BEN | GPIO<br>AEN |

|               |                         |             | rw                  |                    |                    |              | rw       | rw          | rw          | rw          | rw               | rw          | rw            | rw          | rw          |

Bit 3 **GPIODEN:** IO port D clock enable

Set and cleared by software.

0: IO port D clock disabled

1: IO port D clock enabled

Можно пользоваться готовыми командами:

#### RCC->AHB1ENR |= RCC\_AHB1ENR\_GPIODEN; // включим тактирование порта

Затем необходимо установить режим работы пинов порта как *General purpose output mode*, что означает что контроллер GPIO будет управлять состоянием пина МК. Управление режимом работы пинов МК производится помощью регистра *GPIO port mode register* (*GPIOx\_MODER*) (x = A..I/J/K):

#### 8.4.1 GPIO port mode register (GPIOx\_MODER) (x = A..I/J/K)

Address offset: 0x00

Reset values:

- 0xA800 0000 for port A

- 0x0000 0280 for port B

- 0x0000 0000 for other ports

| 31           | 30          | 29           | 28          | 27           | 26          | 25           | 24          | 23           | 22          | 21           | 20          | 19          | 18          | 17          | 16          |  |

|--------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|-------------|-------------|-------------|-------------|--|

| MODER15[1:0] |             | MODER14[1:0] |             | MODER13[1:0] |             | MODER12[1:0] |             | MODER11[1:0] |             | MODER10[1:0] |             | MODER9[1:0] |             | MODER8[1:0] |             |  |

| rw           | rw          | rw          | rw          | rw          | rw          |  |

| 15           | 14          | 13           | 12          | 11           | 10          | 9            | 8           | 7            | 6           | 5            | 4           | 3           | 2           | 1           | 0           |  |

| MODE         | MODER7[1:0] |              | MODER6[1:0] |              | MODER5[1:0] |              | MODER4[1:0] |              | MODER3[1:0] |              | MODER2[1:0] |             | MODER1[1:0] |             | MODER0[1:0] |  |

| rw           | rw          | rw          | rw          | rw          | rw          |  |

Bits 2y:2y+1 MODERy[1:0]: Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O direction mode.

00: Input (reset state)

01: General purpose output mode

10: Alternate function mode

11: Analog mode

#### // включим ножки 12,13,14,15 на выход

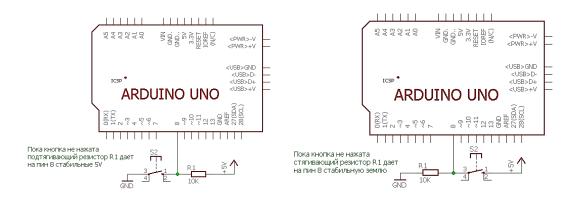

Если записать все нули, то пин будет сконфигурирован как вход. Входы могут работать в одном из трех режимов:

- no pull up/down resistors

- pull-up a resistor connected to high

- pull-down a resistor connected to low

Выходы могут работать в одном из трех режимов:

- open drain a transistor connects to low and nothing else

- open drain, with pull-up a transistor connects to low, and a resistor connects to high

- push-pull a transistor connects to high, and a transistor connects to low (only one is operated at a time)

#### Входы

Подтягивающие резисторы могут быть заданы с помощью регистра:

# 8.4.4 GPIO port pull-up/pull-down register (GPIOx\_PUPDR) (x = A..I/J/K)

Address offset: 0x0C

#### Reset values:

- 0x6400 0000 for port A

- 0x0000 0100 for port B

- 0x0000 0000 for other ports

| 31    | 30                       | 29 | 28           | 27          | 26           | 25          | 24           | 23          | 22           | 21          | 20          | 19          | 18          | 17          | 16 |

|-------|--------------------------|----|--------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|-------------|-------------|-------------|-------------|----|

| PUPDF | UPDR15[1:0] PUPDR14[1:0] |    | PUPDR13[1:0] |             | PUPDR12[1:0] |             | PUPDR11[1:0] |             | PUPDR10[1:0] |             | PUPDR9[1:0] |             | PUPDR8[1:0] |             |    |

| rw    | rw                       | rw | rw           | rw          | rw           | rw          | rw           | rw          | rw           | rw          | rw          | rw          | rw          | rw          | rw |

| 15    | 14                       | 13 | 12           | 11          | 10           | 9           | 8            | 7           | 6            | 5           | 4           | 3           | 2           | 1           | 0  |

| PUPDI | PUPDR7[1:0] PUPDR        |    | R6[1:0]      | PUPDR5[1:0] |              | PUPDR4[1:0] |              | PUPDR3[1:0] |              | PUPDR2[1:0] |             | PUPDR1[1:0] |             | PUPDR0[1:0] |    |

| rw    | rw                       | rw | rw           | rw          | rw           | rw          | rw           | rw          | rw           | rw          | rw          | rw          | rw          | rw          | rw |

Bits 2y:2y+1 **PUPDRy[1:0]:** Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O pull-up or pull-down

00: No pull-up, pull-down

01: Pull-up

10: Pull-down

11: Reserved

Подтягивающий резистор нужен, чтобы гарантировать на логическом входе, с которым соединён проводник, высокий (в первом случае) либо низкий (во втором случае) уровень пока вход разомнут, чтобы не оставлять его в «подвешенном» состоянии.

#### Выходы

Блок GPIO позволяет применить дополнительные настройки для выходных пинов порта. Данные настройки производятся в регистрах:

- GPIO port output type register (GPIOx\_OTYPER) задается тип выхода push-pull или open-drain. По умолчанию двухтактный (push-pull) для каждой ножки

- GPIO port output speed register (GPIOx\_OSPEEDR) задается скорость работы выхода

#### 8.4.2 GPIO port output type register (GPIOx\_OTYPER) (x = A..I/J/K)

Address offset: 0x04

Reset value: 0x0000 0000

| 31   | 30       | 29   | 28   | 27   | 26   | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|------|----------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|      | Reserved |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| 15   | 14       | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| OT15 | OT14     | OT13 | OT12 | OT11 | OT10 | OT9 | OT8 | OT7 | OT6 | OT5 | OT4 | OT3 | OT2 | OT1 | ОТ0 |

| rw   | rw       | rw   | rw   | rw   | rw   | rw  | rw  | rw  | rw  | rw  | rw  | rw  | rw  | rw  | rw  |

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 **OTy**: Port x configuration bits (y = 0..15)

These bits are written by software to configure the output type of the I/O port.

0: Output push-pull (reset state)

1: Output open-drain

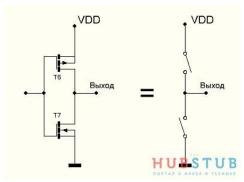

Open drain – используется для подключения нескольких устройств по принципу ИЛИ. В режиме push-pull такое подключение невозможно. Push-pull интерфейсах, конфигурация чаще всего используется В однонаправленные линии (передача по линии осуществляется только в одном направлении - SPI, UART и т.д.). В Open drain в большинстве случаев используется внешний подтягивающий резистор (есть микроконтроллеры, которые обеспечивают внутренние подтягивающие резисторы ДЛЯ конфигураций с Open drain). Выходы с Open drain чаще всего используются в интерфейсах связи, где несколько устройств подключены к одной линии (например, I2C, One-Wire и т.д.). Когда все выходы устройств, подключенных к линии, находятся в состоянии Hi-Z (high impedance – используется только транзистор), они все «видят» один уровень высокий (для случая open-drain, with pull-up) или низкий.

Режим push-pull: по сути, он состоит из двух ключей, один подтягивает вывод к питанию, другой к земле.

Режим **open-drain**. Справа open-drain, with pull-up

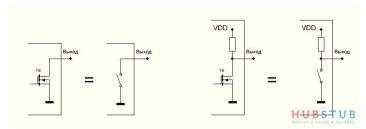

Рассмотрим два выхода push-pull соединенных с разной полярностью. Из-за конфликта уровней один из выходов просто выгорит, так как ток, возникший из-за разности потенциалов, ничем не ограничен.

А теперь так же соединим два вывода ОО.

Здание скорости. Это задается только для пинов, настроенных как выходы. Использование чрезмерно высокой скорости может вызвать звон и электромагнитные помехи на выходах, поэтому важно использовать минимальную скорость, необходимую для вашего приложения:

# 8.4.3 GPIO port output speed register (GPIOx\_OSPEEDR) (x = A..I/J/K)

Address offset: 0x08

#### Reset values:

- 0x0C00 0000 for port A

- 0x0000 00C0 for port B

- 0x0000 0000 for other ports

| 31                 | 30            | 29                 | 28            | 27                 | 26       | 25                 | 24       | 23                 | 22       | 21                 | 20       | 19                | 18          | 17                | 16         |

|--------------------|---------------|--------------------|---------------|--------------------|----------|--------------------|----------|--------------------|----------|--------------------|----------|-------------------|-------------|-------------------|------------|

| OSPEEDR15<br>[1:0] |               | OSPEEDR14<br>[1:0] |               | OSPEEDR13<br>[1:0] |          | OSPEEDR12<br>[1:0] |          | OSPEEDR11<br>[1:0] |          | OSPEEDR10<br>[1:0] |          | OSPEEDR9<br>[1:0] |             | OSPEEDR8<br>[1:0] |            |

| rw                 | rw            | rw                 | rw            | rw                 | rw       | rw                 | rw       | rw                 | rw       | rw                 | rw       | rw                | rw          | rw                | rw         |

| 15                 | 14            | 13                 | 12            | 11                 | 10       | 9                  | 8        | 7                  | 6        | 5                  | 4        | 3                 | 2           | 1                 | 0          |

| OSPEE              | OSPEEDR7[1:0] |                    | OSPEEDR6[1:0] |                    | DR5[1:0] | OSPEE              | DR4[1:0] | OSPEE              | DR3[1:0] | OSPEE              | DR2[1:0] | OSPE<br>[1        | EDR1<br>:0] |                   | EDR0<br>0] |

| rw                 | rw            | rw                 | rw            | rw                 | rw       | rw                 | rw       | rw                 | rw       | rw                 | rw       | rw                | rw          | rw                | rw         |

Bits 2y:2y+1 **OSPEEDRy[1:0]:** Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O output speed.

- 00: Low speed

- 01: Medium speed

- 10: High speed

- 11: Very high speed

Note: Refer to the product datasheets for the values of OSPEEDRy bits versus V<sub>DD</sub> range and external load.

- Low speed- 2 MHz

- Medium speed 25 MHz

- High speed 50 MHz

- Very high speed 100 MHz

# Пример программного кода

```

//----GPIO

#define

PORT D ON

(1 << 3)

(0x1 << 6) // 01: General purpose output

#define

GPIOD MODE MSK

mode, for each pin of port there are 2 bits of register GPIOx->MODER

#define

GPIOD MODE CLEAR MSK

(0x3 << 6)

#define

GPIOD_TYPE_MSK

(0 << 3)

// 0: Output push-pull

(reset state), 1: Output open-drain

#define

GPIOD TYPE CLEAR MSK

(1 << 3)

GPIOD SPEED MSK

#define

(0x0 << 6)

// 00: Low speed, 01:

Medium speed, 10: High speed, 11: Very high speed

#define

GPIOD SPEED CLEAR MSK

(0x3 << 6)

#define

// 00: No pull-up,

GPIOD PPUDR MSK

(0x0 << 6)

pull-down, 01: Pull-up, 10: Pull-down

#define

GPIOD PPUDR CLEAR MSK (0x3 << 6)

#define

GPIOD PD3 ON

(1 << 3)

#define

GPIOD PD3 OFF

~(GPIOD PD3 ON)

// Bits 15:0 LCKy: Port x lock

#define

GPIOD LCKR MSK

(0x0)

bit y (y = 0...15)

#define

GPIOD_LCKR_CLEAR_MSK

(0x0001FFFF)

// AFRy: Alternate function

#define

GPIOD AFR1 MSK

(0x0)

selection for port x bit y (y = 0...7)

(0xFFFFFFF) // 0000: AF0 - SYS

#define

GPIOD AFR1 CLEAR MSK

```

```

(0x0)

#define GPIOD AFR2 MSK

// AFRy: Alternate

function selection for port x bit y (y = 8..15)

#define GPIOD_AFR2_CLEAR_MSK (0xFFFFFFFF) // 0000: AF0 - SYS

RCC->AHB1ENR |= PORT D ON; // activate controller GPIOD - it is

on AHB1 port

GPIOD->MODER &= ~GPIOD MODE CLEAR MSK;

GPIOD->MODER |= GPIOD MODE MSK;

//----

GPIOD->OTYPER &= ~GPIOD_TYPE_CLEAR_MSK;

GPIOD->OTYPER |= GPIOD TYPE MSK;

//----

GPIOD->OSPEEDR &= ~GPIOD_SPEED_CLEAR_MSK;

GPIOD->OSPEEDR |= GPIOD SPEED MSK;

//----

GPIOD->PUPDR &= ~GPIOD PPUDR CLEAR MSK;

GPIOD->PUPDR |= GPIOD PPUDR MSK;

//----

GPIOD->LCKR &= ~GPIOD LCKR CLEAR MSK;

GPIOD->LCKR |= GPIOD LCKR MSK;

//-----

GPIOD->AFR[0] &= ~GPIOD_AFR1_CLEAR_MSK;

GPIOD->AFR[1] &= ~GPIOD AFR2 CLEAR MSK;

GPIOD->AFR[0] |= GPIOD AFR1 MSK;

GPIOD->AFR[1] |= GPIOD_AFR2_MSK;

//----

GPIOD->ODR &= GPIOD_PD3_OFF;

```

# Задание на работу

- 1. Написать программный код на языке Си настройки системы тактирования RCC (используется внешний тактовый генератор с частотой 25 МГц), базового таймера TIM6 (прерывание каждую секунду) и контроллера ввода-вывода GPIOD (пин 3).

- 2. Написать программный код на языке Си управления выходным сигналом на третьей ножке (пин 3) контроллера ввода-вывода GPIOD: снятие и установка напряжения на ножке 1 раз в секунду (время должен

отсчитывать таймер TIM6) – эффект мигания лампочки.

# Наблюдаемые параметры

1. Контроль появления импульсов на ножке пина 3 GPIOD с помощью цифрового осциллографа.