#### 2.3 Поцессоры современных компьютеров

## 2.3.1 Процессоры с архитектурой 80x86 и Pentium

Родоначальником архитектуры процессоров Intel x86 является процессор Intel 8086 (1978 год). Intel 8086 представляет собой 16-битовую архитектуру со всеми внутренними регистрами, имеющими 16-битовую разрядность. К процессорам этого класса относятся микропроцессоры: Intel 80286 (24 битная архитектура), 80386 (32 битная архитектура), 80486 (32-битовые процессоры с внутренней кэш-памятью и встроенным сопроцессором (только DX)), Pentium, Pentium II и т.д.

Особенностью этих процессоров является преемственность на уровне машинных команд: программы, написанные для младших моделей процессоров, без каких-либо изменений могут быть выполнены на более старших моделях. При этом базой является система команд процессора 8086.

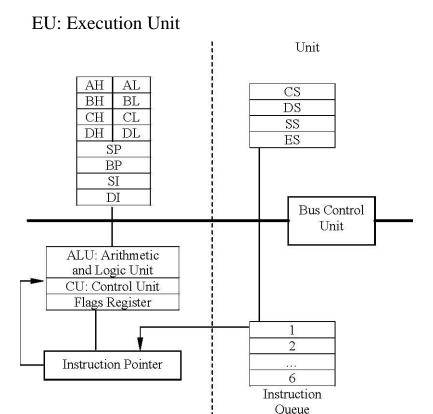

Структуру центрального процессора Intel 8086 можно разделить на два логических блока (рис.2.4):

- блок исполнения (EU:Execution Unit);

- . блок интерфейса шин (BIU:Bus Interface Unit). В состав EU входят: арифметическо-логическое устройство ALU, устройство управления CU и десять регистров. Устройства блока EU обеспечивают обработку команд, выполнение арифметических и логических операций.

Блок BIU включает устройство управления шинами, блок очереди команд, регистры сегментов и предназначен для выполнения следующих функций:

- . управление обменом данными с EU, памятью и внешними устройствами ввода/вывода;

- адресация памяти;

- . выборка команд (осуществляется с помощью блока очереди команд Queue, который позволяет выбирать команды с упреждением).

Рис. 2.4. Структура микропронессора Intel 8086

Регистры микропроцессора имеют следующее назначение:

*Регистры общего назначения* — это 16-разрядные регистры AX, BX, CX, DX, каждый из которых состоит из двух 8-разрядных регистров, например, AX состоит из AH (старшая часть) и AL (младшая часть).

В общем случае функция, выполняемая тем или иным регистром, определяется командами, в которых он используется. При этом с каждым регистром связано некоторое стандартное его значение:

- . регистр АХ служит для временного хранения данных (регистр аккумулятор), часто используется при выполнении операций сложения, вычитания, сравнения и других арифметических и логических операций;

- . регистр ВХ служит для хранения адреса некоторой области памяти (базовый регистр), а также используется как вычислительный регистр;

- . регистр СХ иногда используется для временного хранения данных, но в основном служит счетчиком, в нем хранится число повторений одной команды или фрагмента программы;

- . регистр DX используется главным образом для временного хранения данных, часто служит средством пересылки данных между разными программными системами, а также используется в качестве расширителя

аккумулятора для вычислений повышенной точности и при умножении и делении.

*Регистры указатели* – это 16-разрядные регистры BP (указатель базы), SI (индекс источника), DI (индекс результата), SP (указатель стека), IP (указатель команд).

Регистры SI, DI, BP используются в командах для хранения адресов памяти. При адресации памяти эти регистры могут быть использованы в различных комбинациях, что определяет различные режимы адресации.

Регистр SP определяет смещение текущей вершины стека. Указатель стека SP вместе с сегментным регистром стека SS используется для формирования физического адреса стека.

Регистр указателя команд IP, иначе называемый регистром счетчика команд и хранит адрес ячейки памяти, содержащей начало следующей команды. Микропроцессор использует регистр IP совместно с регистром CS для формирования физического адреса очередной выполняемой команды

*Регистры сегментов* — это 16-разрядные регистры, которые позволяют организовать память в виде совокупности четырех различных сегментов.

- . CS регистр программного сегмента (сегмента кода) определяет местоположение части памяти, содержащей программу, то есть выполняемые процессором команды;

- . DS регистр информационного сегмента (сегмента данных) идентифицирует часть памяти, предназначенной для хранения данных;

- . SS регистр стекового сегмента (сегмента стека) определяет часть памяти, используемой как системный стек;

- . ES регистр расширенного сегмента (дополнительного сегмента) указывает дополнительную область памяти, используемую для хранения данных.

Регистр флагов — это 16-разрядный регистр, содержащий биты, определяющие код условия, установленный последней выполненной командой или состояние микропроцессора. Эти биты называются флагами.

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5 | 4  | 3 | 2  | 1 | 0  |

|----|----|----|----|----|----|----|----|----|----|---|----|---|----|---|----|

| X  | X  | X  | X  | OF | DF | IF | TF | SF | ZF | X | AF | X | PF | X | CF |

Биты регистра флагов имеют следующее назначение: OF (признак переполнения) — равен единице, если возникает арифметическое переполнение, то есть когда объем результата превышает размер ячейки назначения; DF (признак направления) — устанавливается в единицу для автоматического декремента в командах обработки строк, и в ноль — для

инкремента; IF (признак разрешения прерывания) — прерывания разрешены, если IF=1. Если IF=0, то распознаются лишь немаскированные прерывания; TF (признаков трассировки) — если TF=1, то процессор переходит в состояние прерывания INT 3 после выполнения каждой команды; SF (признак знака) — SF=1, когда старший бит результата равен единице. Иными словами, SF=0 для положительных чисел, и SF=1 для отрицательных чисел; ZF (признак нулевого результата) — ZF=1, если результат равен нулю; AF (признак дополнительного переноса) — этот флаг устанавливается в единицу во время выполнения команд десятичного сложения и вычитания при возникновении переноса или заема между полубайтами;

PF (признак четности) — этот признак устанавливается в единицу, если результат имеет четное число единиц;

CF (признак переноса) — этот флаг устанавливается в единицу, если имеет место перенос или заем из старшего бита результата, он полезен для произведения операций над числами длиной в несколько слов, которые сопряжены с переносами и заемами из слова в слово;

X – зарезервированные биты.

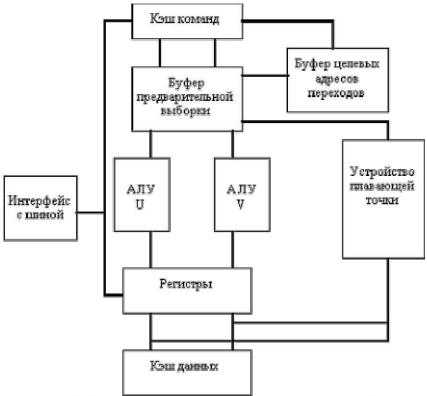

Архитектура микропроцессора Pentium значительно отличается от приведенной выше, что обуславливает следующие преимущества указанного класса процессоров:

- . двухпотоковая суперскалярная организация, допускающая параллельное выполнение пары простых команд;

- . наличие двух независимых двухканальных множественно-ассоциативных кэшей для команд и для данных, обеспечивающих выборку данных для двух операций в каждом такте;

- . динамическое прогнозирование переходов;

- . конвейерная организация устройства плавающей точки с 8 ступенями;

- двоичная совместимость с существующими процессорами семейства 80х86. Упрощенная структура процессора Pentium представлена на рис. 2.5. Прежде всего, новая микроархитектура этого процессора базируется на идее суперскалярной обработки. Основные команды распределяются по двум независимым исполнительным устройствам (конвейерам U и V). Конвейер U может выполнять любые команды семейства х86, включая целочисленные команды и команды с плавающей точкой. Конвейер V предназначен для выполнения простых целочисленных команд и некоторых команд с плавающей точкой. Команды могут направляться в каждое из этих устройств

одновременно, причем при выдаче устройством управления в одном такте пары команд более сложная команда поступает в конвейер U, а менее сложная - в конвейер V (при этом, однако, не все команды совместимы). Остальные устройства процессора предназначены для снабжения конвейенеобходимыми командами и данными. В процессоре используется раздельная кэш-память команд и данных, что обеспечивает независимость обращений. За один такт из каждой кэш-памяти могут считываться два слова. Для повышения эффективности перезагрузки кэшпамяти в процессоре применяется 64-битовая внешняя шина данных. В предусмотрен механизм динамического прогнозирования направления переходов. С этой целью на кристалле размещена небольшая кэш-память, которая называется буфером целевых адресов переходов (ВТВ), и две независимые пары буферов предварительной выборки команд (по два 32-битовых буфера на каждый конвейер). Буфер целевых адресов переходов хранит адреса команд, которые находятся в буферах предварительной выборки. Работа буферов предварительной выборки организована таким образом, что в каждый момент времени осуществляется выборка команд только в один из буферов соответствующей пары. При обнаружении в потоке команд операции перехода вычисленный адрес перехода сравнивается с хранящимися В буфере BTB. В случае предсказывается, что переход будет выполнен, и разрешается работа другого бу-фера предварительной выборки, который начинает выдавать команды для выполнения в соответствующий конвейер. При несовпадении считается, что переход выполняться не будет и буфер предварительной выборки не переключается, продолжая обычный порядок

выдачи команд. Это позволяет избежать простоев конвейеров при правильном прогнозе направления перехода.

Рис. 2.5. Упрошенная структура процессора Pentium

Совместимые с Intel процессоры выпускают следующие производители Advanced Micro Devices (AMD), Cyrix Corp и NexGen.

# 2.3.2 Особенности процессоров с архитектурой SPARC

Масштабируемая процессорная архитектура (SPARC - Scalable Processor Architecture) компании Sun Microsystems является наиболее широко распространенной RISC-архитектурой, и доминирует на рынке UNIX-рабочих станций и серверов. Процессоры с архитектурой SPARC лицензированы и изготавливаются компанииями Texas Instruments, Fujitsu, Philips и др.

Первоначально архитектура SPARC была разработана с целью упрощения реализации 32-битового процессора. В последствии по мере улучшения технологии изготовления интегральных схем она постепенно развивалось в 64-битовую архитектуру.

В отличие от большинства RISC архитектур SPARC использует регистровые окна, которые обеспечивают удобный механизм передачи параметров между программами и возврата результатов. Архитектура SPARC была первой коммерческой разработкой, реализующей механизмы отложенных переходов и аннулирования команд. Это давало компилятору большую свободу заполнения времени выполнения команд перехода командой, которая выполняется в случае выполнения условий перехода и игнорируется в случае, если условие перехода не выполняется.

Развитием процессоров со SPARC архитектурой являются процессоры SuperSPARC HyperSPARC, MicroSPARC.

Например, в процессорах SuperSPARC реализован принцип суперскалярной обра-ботки, позволяющий в зависимости от смеси команд обрабатывать до трех команд за один машинный такт. SPARC-процессор имеет сбалансированную производительность на опеациях с фиксированной и плавающей точкой, раздельный внутренний кэш большой емкости, раздельные конвейеры целочисленной и вещественной арифметики и при одинаковой тактовой частоте обеспечивает производительность приблизительно в два раза большую, чем процессор Pentium.

#### 2.3.3 Особенности процессоров с архитектурой PA-RISC

Основой разработки современных изделий Hewlett-Packard является архитектура PARISC. Примерами таких процессоров могут служить PA-7100 и PA-7200, являющиеся основой построения семейства рабочих станций и семейства бизнес-серверов HP 9000 Series.

Особенностью архитектуры PA-RISC является внекристальная реализация кэша, что позволяет реализовать различные объемы кэш-памяти и оптимизировать конструкцию в зависимости от условий применения. Хранение команд и данных осуществляется в раздельных кэшах, причем процессор соединяется с ними с помощью высокоскоростных 64-битовых шин.

Конструктивно на кристалле PA-7100 размещены целочисленный процессор, процессор для обработки чисел с плавающей точкой, устройство управления кэшем, унифицированный буфер TLB, устройство управления, а также ряд интерфейсных схем.

#### 2.3.4 Особенности процессоров с архитектурой МС88110

Процессор 88110 компании Motorola относится к разряду суперскалярных RISC-процессоров. Основные особенности этого процессора связаны с использованием принципов суперскалярной обработки, двух восьмипортовых регистровых файлов, десяти независимых исполнительных устройств, больших по объему внутренних кэшей и широких магистралей данных.

Процессор имеет 10 исполнительных устройств, которые работают одновременно и независимо, и два регистровых файла. Файл регистров общего назначения имеет 32-битовую организацию. Расширенные регистры плавающей точки имеют 80-битовую организацию. Центральное место архитектуры этого процессора занимает шина операндов (шесть 80-битовых шин), соединяющая регистровые файлы и исполнительные устройства.

Суперскалярная архитектура процессора базируются на реализации возможности завершения команд не в порядке их поступления для выполнения, что позволяет существенно увеличить производительность, однако приводит к некоторым сложностям организации точного прерывания.

При построении многопроцессорной системы все процессоры и основная память размещаются на одной плате. Для обеспечения хорошей производительности системы каждый процессор в такой конфигурации снабжается кэш-памятью второго уровня большой емкости.

# 2.3.5 Особенности процессоров с архитектурой MIPS

Архитектура MIPS компании MIPS Technology была одной из первых RISC-архитектур, получившей признание со стороны промышленности. К процессорам этого класса относятся 32-битовые R2000 и R3000, которые в течение достаточно длительного времени служили основой для построения рабочих станций и серверов компаний Silicon Graphics, Digital, Siemens Nixdorf и др., процессоры с64-битовой архитектурой R4000 и R4400, а также процессоры R10000, которые наряду с 64-разрядными шинами оснащены и 128-разрядными шинами, что значительно увеличивает их производительность.

В процессоре R10000 имеются пять полностью независимых исполнительных устройств: два целочисленных АЛУ, два основных устройства плавающей точки и два вторичных устройства плавающей точки, которые работают с длинными операциями, такими как деление и вычисление квадратного корня.

Процессор R10000 допускает способа организации два многопроцессорной системы. Один из способов связан с созданием специального внешнего интерфейса для каждого процессора системы. Второй способ предназначен достижения максимальной ДЛЯ производительности при минимальных затратах. Он подразумевает использование от двух до четырех процессоров, объединенных шиной Claster Bus. В этом случае необходим только один внешний интерфейс для взаимодействия с другими ресурсами системы.

## 2.3.6 Особенности процессоров с архитектурой Alpha

В настоящее время семейство микропроцессоров с архитектурой Alpha представлено несколькими кристаллами, имеющими различные диапазоны производительности, работающие с разной тактовой частотой и рассеивающие разную мощность.

Типичным представителем указанной архитектуры является разрядный микропроцессор Alpha компании DEC. Он представляет собой RISC-процессор в однокристальном исполнении, в состав которого входят устройства целочисленной и плавающей арифметики, а также кэш-память. с учетом реализации передовых проектировался увеличения производительности, включая конвейерную организацию всех функциональных устройств, одновременную выдачу нескольких команд для выполнения, a также средства организации симметричной многопроцессорной обработки.

Ключевыми моментами для реализации высокой производительности процессоров этой архитектуры является суперскалярный режим работы процессора, обеспечивающий выдачу для выполнения до четырех команд в каждом такте, высокопроизводительная неблокируемая подсистема памяти с быстродействующей кэш-памятью первого уровня, большая, размещенная на кристалле, кэш-память второго уровня и уменьшенная задержка выполнения

## 2.3.7 Особенности процессоров с архитектурой POWER и PowerPC

Архитектура POWER компании IBM во многих отношениях представляет собой традиционную RISC-архитектуру. Она придерживается наиболее важных отличительных особенностей RISC: фиксированной длины команд, архитектуры регистр-регистр, простых способов адресации, простых (не требующих интерпретации) команд, большого регистрового файла и трехоперандного (неразрушительного) формата команд. Однако архитектура POWER имеет также несколько дополнительных свойств, которые отличают ее от других RISC-архитектур.

Во-первых, набор команд был основан на идее суперскалярной обработки. В базовой архитектуре команды распределяются по трем устройствам: независимым исполнительным устройству переходов, устройству с фиксированной точкой и устройству с плавающей точкой. Команды могут направляться в каждое из этих устройств одновременно, где они могут выполняться одновременно и заканчиваться не в порядке поступления. Для увеличения уровня параллелизма, который может быть достигнут на практике, архитектура набора команд определяет для каждого из устройств независимый набор регистров. Это минимизирует связи и синхронизацию, требуемые между устройствами, позволяя тем самым исполнительным устройствам настраиваться на динамическую смесь команд. Любая связь по данным, требующаяся между устройствами, должна анализироваться компилятором, который может спланировать. Следует отметить, что это только концептуальная модель. Любой конкретный процессор с архитектурой POWER может рас-сматривать любое из концептуальных устройств как множество исполнительных устройств для поддержки дополнительного параллелизма команд. Но существование модели приводит к согласованной разработке набора команд, который естественно поддерживает степень параллелизма по крайней мере равную трем.

Во-вторых, архитектура POWER расширена несколькими "смешанными" командами для сокращения времен выполнения. Возможно единственным недостатком технологии RISC по сравнению с CISC, является то, что иногда она использует большее количество команд для выполнения одного и того же задания. Было обнаружено, что во многих случаях увеличения размера кода можно избежать путем небольшого расширения набора команд, которое вовсе не означает возврат к сложным командам, подобным командам CISC. Например, значительная часть увеличения программного кода была обнаружена в кодах пролога и эпилога, связанных с сохранением и восстановлением регистров во время вызова процедуры. Чтобы устранить этот фактор IBM ввела команды "групповой загрузки и записи", которые обеспечивают пересылку нескольких регистров в/из памяти с помощью единственной команды.

Архитектура POWER обеспечивает также несколько других способов сокращения времени выполнения команд такие как: обширный набор команд для манипуляции битовыми полями, смешанные команды умножения сложения с плавающей точкой, установку регистра условий в качестве побочного эффекта нормального выполнения команды и команды загрузки и записи строк (которые работают с произвольно выровненными строками байтов).

Третьим фактором, который отличает архитектуру POWER от многих других RISC-архитектур, является отсутствие механизма "задержанных переходов". Обычно этот механизм обеспечивает выполнение команды, следующей за командой условного перехода, перед выполнением самого перехода. Этот механизм эффективно работал в ранних RISC-машинах для заполнения "пузыря", появляющегося при оценке условий для выбора направления перехода и выборки нового потока команд. Однако в более продвинутых, суперскалярных машинах, этот механизм может оказаться неэффективным, поскольку один такт задержки команды перехода может привести к появлению нескольких "пузырей", которые не могут быть покрыты с помощью одного архитектурного слота задержки. Почти все такие машины, чтобы устранить влияние этих "пузырей", вынуждены вводить дополнительное оборудование (например, кэш-память адресов переходов). В таких машинах механизм задержанных переходов становится не только мало эффективным, но и привносит значительную сложность в логику обработки последовательности команд. Вместо этого архитектура переходов POWER была организована для поддержки методики "предварительного просмотра переходов" (branch-lockahead) "свертывания условных И методики переходов" (branch-folding).

По данным IBM процессор POWER требует менее одного такта для выполнении одной команды по сравнению с примерно 1.25 такта у процессора MC Motorola, 1.45 такта у процессора SPARC, 1.8 такта у Intel i486DX и 1.8 такта Hewlett-Packard PA-RISC.

Дальнейшее развитее процессоров POWER дало новое направление а архитектуре – PowerPC компаний Motorola, Apple и IBM.

РоwerPC базируется на платформе POWER в дешевой конфигурации. В архитектурном плане основные отличия этих двух разработок заключаются лишь в том, что системы PowerPC используют однокристальную реализацию архитектуры POWER, изготавливаемую компанией Motorola, в то время как большинство систем POWER используют многокристальную реализацию. Имеется несколько вариаций процессора PowerPC, обеспечивающих потребности портативных изделий и настольных рабочих станций, но это не ис-ключает возможность применения этих процессоров в больших системах.