# F.A. Gubarev, M.E. Nakonechnaya

# DIGITAL DEVICES

TOMSK POLYTECHNIC UNIVERSITY

F.A. Gubarev, M.E. Nakonechnaya

# **DIGITAL DEVICES**

# **Practical Course**

Recommended for publishing as a study aid by the Editorial Board of Tomsk Polytechnic University

Tomsk Polytechnic University Publishing House 2013

UDC 004.31(075.8) BBC 32.973.2я73 G93

#### Gubarev F.A.

G93

Digital Devices. Practical Course: study aid / F.A. Gubarev, M.E. Nakonechnaya; Tomsk Polytechnic University. – Tomsk: TPU Publishing House, 2013. – 112 pp.

In the Practical Course the main operation principles of digital automatics units are discussed. The complex of practical exercises is offered students to consolidate the theory and skills of electronic circuits design on the basis of digital devices. It contains nine practical works accompanied by methodical instructions and required theoretical knowledge.

This study aid is intended for the students, studying courses "Digital Devices" and "Microprocessor Technique". It also can be helpful for students of all specialities related to Electrophysics and Electronic Equipment.

UDC 004.31(075.8) BBC 32.973.2я73

#### Reviewers

PhD, associated professor of Tomsk State Pedagogical University Dean of the Faculty of Foreign Languages *I.E. Vysotova*

PhD, associated professor of the Tomsk Polytechnic University D.N. Ogorodnikov

PhD, senior staff scientist of V.E. Zuev Institute of Atmospheric Optics D.V. Apeksimov

© STE HPT TPU, 2013

© Gubarev F.A., Nakonechnaya M.E., 2013

© Design. Tomsk Polytechnic University Publishing House, 2013

# INTRODUCTION

Nowadays it is hard to imagine our lives without modern digital devices. In the morning digital alarm-clocks wake people up, digital watches inform us about the beginning of a new day and are even able to play brisk melodies. A microwave oven warms our breakfast up measuring the time till its ready. When we go to our work we often use elevators, which let us easily and quickly reach the required floor. A great many of traffic lights make it safe to move around the city.

It is also impossible to imagine modern enterprises without personal computers and workstations. Here huge quantities of information which can be provided for a consumer on demand are stored. This is only a small number of applications of digital circuits – logic gates, registers, counters, timers, switches, decoders, adders, converters, etc. They make up all the devices considered above – digital watches, timers, lift and traffic lights control circuits, computers.

The first and the most essential factor for the constructed circuits to operate without fail and provide our lives with comfort is to know the physical principles of the simplest digital devices functioning and the methods of design of complex systems made on their basis. Digital electronics plays an important role in providing high reliability of the created automatic and computer-aided systems, which control objects, processes and manufacturing systems.

It is obvious that the modern digital devices are more and more seldom designed using simple discrete integrated circuits (IC) – ordinary logic gates, counters, registers, and flip-flop. At the same time all these elements being the components of more complicated circuits form the basis of programmable logic device (PLD), microcontrollers, and microprocessors. Therefore, the knowledge of fundamentals of digital technique is necessary when studying the disciplines connected with microprocessor-based system.

This teaching aid is a laboratory practical course for the discipline named 'Digital devices'. The book contains methodical guidelines for nine lab works covering three main course units: basic logic gates, combinational logic devices (multiplexers, decoders, arithmetic units), and sequential logic devices (flip-flops, counters, registers). Every lab work is supplied with theoretical background. If a student wants to check his knowledge of the studied material, he is offered some questions at the end of each work.

Methodical instructions presented here and logic circuits recommended for studying require a laboratory bench for circuits assembling and connecting of the required pins of ICs. The commutation process on the pinboard can be done either manually or by means of computer-aided systems.

The practical classes in 'Digital devices' are given at Industrial and Medical Electronics department of Tomsk Polytechnic University using a full-scale modelling system of electronic circuits, which was designed and produced at the department [1, 2]. The laboratory module UIK-1 has a set of slots for placing DIP14  $\mu$  DIP16 integrated circuits, and also a kit of built-in elements (pulse generator, counter, seven-segment display, light-emitting diodes, key buttons, and pull-up and pull-down resistors). The module is connected with the personal computer through USB. The electronic circuit is represented at the screen of the personal computer graphically with the help of the relevant software. The circuit synthesis is executed directly in the module. Such modelling environment let us observe signals at any pin of a real IC with an oscilloscope.

The given teaching aid is based on the lab work instructions [3] which were worked out for the course 'Digital devices' previously. The laboratory course was extended for working with the module UIK-1. The description and pin configuration of the ICs used in the lab works are taken from the reference books [4–7] and manufacturer free access datasheets [8]. Some information about the operational principle of discussed devices you can find in [9–12].

# Lab 1

# ELECTRONIC CIRCUITS SYNTHESIS ACCORDING TO THE GIVEN FUNCTION

#### **1.1 OBJECTIVES**

The lab work acquaints students with basic logic elements and their functions. A widespread series ICs KR1533 (analog SN74ALS) is chosen as an example. The work also helps to develop the skills in minimizing logic functions and circuit synthesis in various element bases.

#### **1.2 PRE-LAB TASKS**

1. Acquaint with the operational principles and pin configuration of the ICs KR1533LA1 (SN74ALS20AN), KR1533LA3 (SN74ALS00AN), KR1533LA4 (SN74ALS10AN), KR1533LE4 (SN74ALS27AN), and KR1533LE1 (SN74ALS02N).

2. Study the aspects of simplifying Boolean functions (BF).

3. Conduct BF minimization by Karnaugh map method according to the lecturer's task. Obtain the minimized algebraic expression in the disjunctive normal form (DNF).

4. Implement the obtained function using NAND universal gates.

5. Present a voltage diagram for the given function; show the time intervals when critical races are possible to emerge.

6. Implement the function on the basis of NOR universal gates.

7. Present voltage diagrams for the given function; show the time intervals when critical races are possible to emerge.

## **1.3 BASIC THEORY**

Any digital computer consists of logic circuits. These are circuits which can be only in two states – either 'logic zero' or 'logic one'. Any expression (including a word) which can be characterized as 'true' or 'false' is assumed as logic zero or logic one. In electronic engineering logic 0 and 1 are the certain states of electric circuits. For example, if we talk about logic elements and circuits carried on TTL-technology (transistor-transistor logic), logic 0 will mean voltage range from 0 to +0.4 V, and logic 1 – from +2.4 to +5 V.

The operation of logic circuits is characterized by a special mathematical tool called Boolean algebra or logical algebra. Boolean algebra was developed by an English mathematician and logician George Boole (1815–

1864) and is the fundamental of all methods of logical expressions simplification.

## 1.3.1 Basic postulates of Boolean algebra

Laws for a single variable

$$X + 0 = X$$

$$X \times 0 = 0$$

$$X + \overline{X} = 1$$

$$X + 1 = 1$$

$$X \times 1 = X$$

$$\overline{X} = X$$

$$\overline{X} = X$$

Laws for two and more variables

1. Commutative law:

$\begin{aligned} X+Y+Z &= Y+X+Z = Z+X+Y, \\ X\times Y\times Z &= Y\times X\times Z = Z\times X\times Y. \end{aligned}$

2. Associative law:

$$X + Y + Z = (X + Y) + Z = (Z + Y) + X,$$

$$X \times Y \times Z = (X \times Y)Z = (Z \times Y)X.$$

3. Distributive law:

$$X(Y+Z) = X \times Y + X \times Z,$$

$$X + (Y \times Z) = (X + Y)(X + Z).$$

4. Absorption law:

$$X + X \times Y = X(1+Y) = X,$$

$$X(X+Y) = X + XY = X.$$

5. Sewing law:

$$X \times Y + \overline{X} \times Y = Y(X + \overline{X}) = Y,$$

$$(X + Y)(\overline{X} + Y) = \overline{X} \times X + X \times Y + Y \times \overline{X} + Y \times Y = Y$$

6. Law of dualization (de Morgan's Theorem):

$$\overline{X+Y} = \overline{X} \times \overline{Y},$$

$$\overline{X+Y} = \overline{\overline{X}} \times \overline{\overline{Y}},$$

$$\overline{X\times Y} = \overline{\overline{X}+\overline{Y}},$$

$$X \times Y = \overline{\overline{X}+\overline{Y}}.$$

# 1.3.2 Karnaugh map method

Karnaugh maps are used to facilitate the simplification of Boolean algebra functions. Karnaugh map is a type of truth table representation. Every

cell of the Karnaugh map corresponds to the row of the truth table. Along each axis variable combinations are plotted, and inside the map the value of the function is given.

The purpose of the Karnaugh map is to find out the logical sum of the direct and inverse variable values. For any variable, for example a, the logical sum equals  $a + \bar{a} = 1$ . If a = 0, we have 0+1=1; if a=1, we get 1+0=1. Therefore, when we put this expression in brackets,

$$abc + \overline{abc} = bc(a + \overline{a}) = bc \cdot 1 = bc$$

the sum  $a + \bar{a} = 1$  can be neglected, and the result of the formula will remain the same. This example shows how the simplification of the logical expression on the basis of Karnaugh map works. Tables 1.1–1.3 present Karnaugh maps of different ranks.

Table 1.1

| 2 variable Rarnaugh map |                 |                 |  |  |

|-------------------------|-----------------|-----------------|--|--|

| B/A                     | 0               | 1               |  |  |

| 0                       | $\overline{AB}$ | $A\overline{B}$ |  |  |

| 1                       | $\overline{AB}$ | AB              |  |  |

2-variable Karnaugh man

Table 1.2

3-variable Karnaugh map

| C/AB | 00               | 01               | 11               | 10                          |

|------|------------------|------------------|------------------|-----------------------------|

| 0    | $\overline{ABC}$ | $\overline{ABC}$ | $AB\overline{C}$ | $A\overline{B}\overline{C}$ |

| 1    | $\overline{ABC}$ | $\overline{ABC}$ | ABC              | $A\overline{B}C$            |

Table 1.3

4-variable Karnaugh mapCD/AB0001111

| CD/AB | 00                | 01                                      | 11                           | 10                                      |

|-------|-------------------|-----------------------------------------|------------------------------|-----------------------------------------|

| 00    | $\overline{ABCD}$ | $\overline{AB}\overline{C}\overline{D}$ | $AB\overline{C}\overline{D}$ | $A\overline{B}\overline{C}\overline{D}$ |

| 01    | $\overline{ABCD}$ | $\overline{ABCD}$                       | $AB\overline{C}D$            | $A\overline{B}\overline{C}D$            |

| 11    | $\overline{ABCD}$ | ABCD                                    | ABCD                         | $A\overline{B}CD$                       |

| 10    | $\overline{ABCD}$ | $\overline{ABCD}$                       | $ABC\overline{D}$            | $A\overline{B}C\overline{D}$            |

How to simplify Boolean functions with the help of Karnaugh map

- 1. Algebraic expression in the disjunctive normal form (as a rule, full DNF) is put down.

- 2. According to the number of variables a corresponding rank of Karnaugh map is chosen.

- 3. 1 is put into those cells of the map, whose summands are present in the algebraic expression of the given function.

- 4. Then  $2^n$  neighbouring 1 are joined by the common contour (every contour can only consist of 1, 2, 4...2<sup>n</sup> logic ones)

- 5. In the obtained contours complementary variables are excluded.

- 6. The simplified Boolean function is written down.

Example 1. Function simplification and synthesis in the NAND basis

E.g. BF  $F = AB\overline{C}D + AB\overline{C}\overline{D} + \overline{AB}CD + A\overline{B}CD + ABCD$  is given. Table 1.4 presents the dependence of *F* on variables *A*, *B*, *C* and *D*.

Table 1.4

| Decimal number | A | В | С | D | F |

|----------------|---|---|---|---|---|

| 0              | 0 | 0 | 0 | 0 | 0 |

| 1              | 0 | 0 | 0 | 1 | 0 |

| 2              | 0 | 0 | 1 | 0 | 0 |

| 3              | 0 | 0 | 1 | 1 | 1 |

| 4              | 0 | 1 | 0 | 0 | 0 |

| 5              | 0 | 1 | 0 | 1 | 0 |

| 6              | 0 | 1 | 1 | 0 | 0 |

| 7              | 0 | 1 | 1 | 1 | 0 |

| 8              | 1 | 0 | 0 | 0 | 0 |

| 9              | 1 | 0 | 0 | 1 | 0 |

| 10             | 1 | 0 | 1 | 0 | 0 |

| 11             | 1 | 0 | 1 | 1 | 1 |

| 12             | 1 | 1 | 0 | 0 | 1 |

| 13             | 1 | 1 | 0 | 1 | 1 |

| 14             | 1 | 1 | 1 | 0 | 0 |

| 15             | 1 | 1 | 1 | 1 | 1 |

*Truth table for F-function*

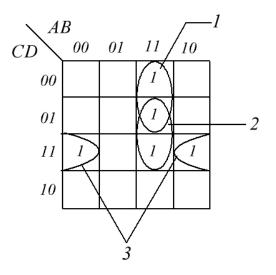

The 4-variable Karnaugh map for the given BF is shown in Fig. 1.1. First contour:  $AB\overline{C}\overline{D} + AB\overline{C}D = AB\overline{C}(D + \overline{D}) = AB\overline{C}$ .

Second contour:  $AB\overline{C}D + ABCD = ABD(C + \overline{C}) = ABD$ .

Third contour:  $\overline{ABCD} + A\overline{B}CD = \overline{B}CD(\overline{A} + A) = \overline{B}CD$ .

Finally, we obtain the simplified expression of the given BF:

$F = AB\overline{C} + ABD + \overline{B}CD.$

According to the Law of dualization (de Morgan's Theorem) the function in the NAND basis can be presented as:

$F = AB\overline{C} + ABD + \overline{B}CD = \overline{AB\overline{C}} \cdot \overline{ABD} \cdot \overline{\overline{B}CD}.$

Fig. 1.1. Karnaugh map for the function in the 1<sup>st</sup> example

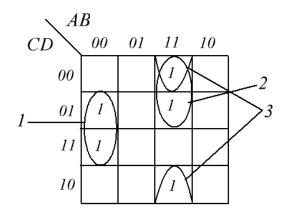

Example 2. Function simplification and synthesis in the NOR basis

E.g. Boolean function  $F = ABC\overline{D} + AB\overline{C}\overline{D} + AB\overline{C}D + \overline{AB}\overline{C}D + \overline{AB}CD$ is given. Table 1.5 presents the dependence of *F* on variables *A*, *B*, *C* and *D*. The four-rank Karnaugh map for the given BF is shown in Fig. 1.2.

Table 1.5

| Decimal number | A | В | С | D | F |

|----------------|---|---|---|---|---|

| 0              | 0 | 0 | 0 | 0 | 0 |

| 1              | 0 | 0 | 0 | 1 | 1 |

| 2              | 0 | 0 | 1 | 0 | 0 |

| 3              | 0 | 0 | 1 | 1 | 1 |

| 4              | 0 | 1 | 0 | 0 | 0 |

| 5              | 0 | 1 | 0 | 1 | 0 |

| 6              | 0 | 1 | 1 | 0 | 0 |

| 7              | 0 | 1 | 1 | 1 | 0 |

| 8              | 1 | 0 | 0 | 0 | 0 |

| 9              | 1 | 0 | 0 | 1 | 0 |

| 10             | 1 | 0 | 1 | 0 | 0 |

| 11             | 1 | 0 | 1 | 1 | 0 |

| 12             | 1 | 1 | 0 | 0 | 1 |

| 13             | 1 | 1 | 0 | 1 | 1 |

| 14             | 1 | 1 | 1 | 0 | 1 |

| 15             | 1 | 1 | 1 | 1 | 0 |

Truth table for F-function

Fig. 1.2. Karnaugh map for the function in the  $2^{nd}$  example

First contour:  $\overline{ABCD} + \overline{ABCD} = \overline{ABD}$ . Second contour:  $AB\overline{CD} + AB\overline{CD} = AB\overline{C}$ . Third contour:  $AB\overline{CD} + ABC\overline{D} = AB\overline{D}$ . Finally, we obtain the simplified expression of the given BF:  $F = \overline{ABD} + AB\overline{C} + AB\overline{D}$ .

According to the de Morgan's Theorem the function in the NOR basic can be presented as

$$F = \overline{ABD} + AB\overline{C} + AB\overline{D} = \overline{\overline{ABD}} + \overline{\overline{ABC}} + \overline{\overline{ABD}} = \overline{\overline{A+B+D}} + \overline{\overline{A}+\overline{B}+C} + \overline{\overline{A}+\overline{B}+D}.$$

1.3.3 Integrated circuits used in the lab work

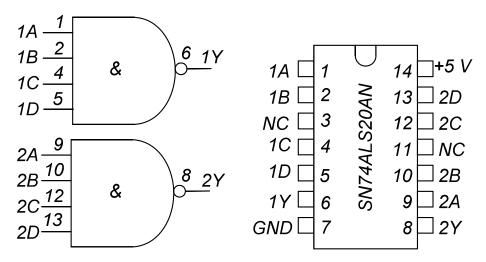

IC KR1533LA1 (SN74ALS20AN) is two 4NAND elements. Fig. 1.3 shows its logic diagram and pin configuration. The operation of one section of the IC is described in table 1.6.

Fig. 1.3. IC KR1533LA1 logic diagram and pin configuration

| Та | abl | e | 1 | 6 |

|----|-----|---|---|---|

|    |     |   |   |   |

|    | Inputs |    |    |               |  |

|----|--------|----|----|---------------|--|

| Al | B1     | Cl | D1 | Outputs<br>F1 |  |

| 0  | 0      | 0  | 0  | 1             |  |

| 0  | 0      | 0  | 1  | 1             |  |

| 0  | 0      | 1  | 0  | 1             |  |

| 0  | 0      | 1  | 1  | 1             |  |

| 0  | 1      | 0  | 0  | 1             |  |

| 0  | 1      | 0  | 1  | 1             |  |

| 0  | 1      | 1  | 0  | 1             |  |

| 0  | 1      | 1  | 1  | 1             |  |

| 1  | 0      | 0  | 0  | 1             |  |

| 1  | 0      | 0  | 1  | 1             |  |

| 1  | 0      | 1  | 0  | 1             |  |

| 1  | 1      | 0  | 0  | 1             |  |

| 1  | 1      | 0  | 1  | 1             |  |

| 1  | 1      | 1  | 0  | 1             |  |

| 1  | 1      | 1  | 1  | 0             |  |

Truth table for one section of IC KR1533LA1

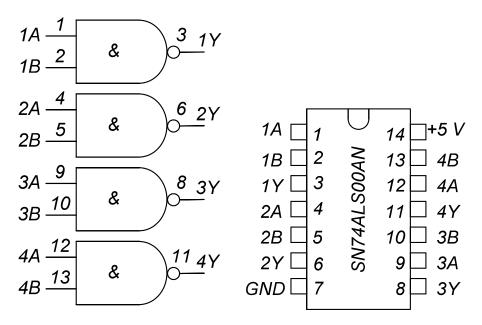

IC KR1533LA3 (SN74ALS00AN) contains four 2NAND elements. Fig. 1.4 shows its logic diagram and pin configuration. The operation of one section of the IC is described in table 1.7.

Fig. 1.4. IC KR1533LA3 logic diagram and pin configuration

Truth table for one section of IC KR1533LA3

| Inputs |           | Output |

|--------|-----------|--------|

| Al     | <i>B1</i> | F1     |

| 0      | 0         | 1      |

| 0      | 1         | 1      |

| 1      | 0         | 1      |

| 1      | 1         | 0      |

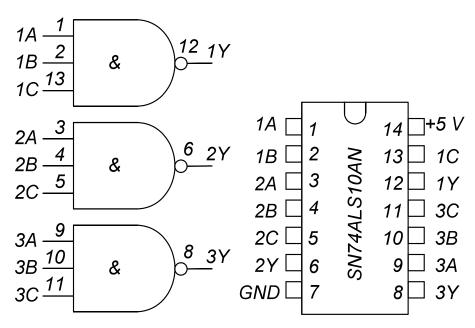

IC KR1533LA4 (SN74ALS10AN) consists of three 3NAND elements. Fig. 1.5 shows its logic diagram and pin configuration. The operation of one section of the IC is described in table 1.8.

Fig. 1.5. IC KR1533LA4 logic diagram and pin configuration

Table 1.8

|    | Inputs |    | Output |

|----|--------|----|--------|

| Al | B1     | Cl | F1     |

| 0  | 0      | 0  | 1      |

| 0  | 0      | 1  | 1      |

| 0  | 1      | 0  | 1      |

| 0  | 1      | 1  | 1      |

| 1  | 0      | 0  | 1      |

| 1  | 0      | 1  | 1      |

| 1  | 1      | 0  | 1      |

| 1  | 1      | 1  | 0      |

## Truth table for one section of IC KR1533LA4

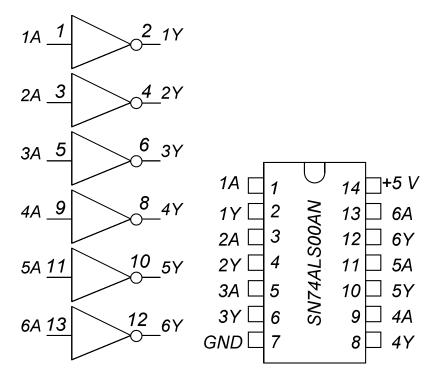

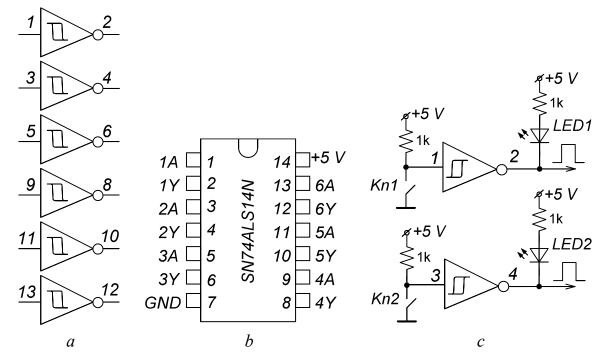

IC KR1533LN1 (SN74ALS04AN) contains six independent inverters (NOT gates). Fig. 1.6 shows its logic diagram and pin configuration.

Fig. 1.6. IC KR1533LN1 logic diagram and pin configuration

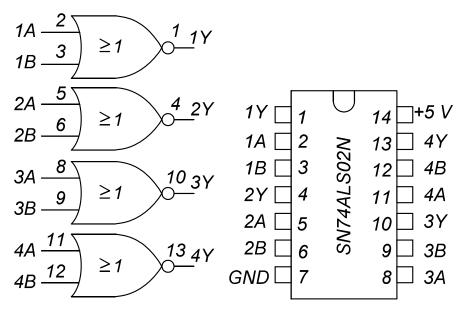

IC KR1533LE1 (SN74ALS02N) is four 2NOR elements. Fig. 1.7 shows its logic diagram and pin configuration. The operation of one section of the IC is described in table 1.9.

Fig. 1.7. IC KR1533LE1 logic diagram and pin configuration

| Inputs |           | Output    |

|--------|-----------|-----------|

| Al     | <i>B1</i> | <i>F1</i> |

| 0      | 0         | 1         |

| 0      | 1         | 0         |

| 1      | 0         | 0         |

| 1      | 1         | 0         |

Truth table for one section of IC KR1533LE1

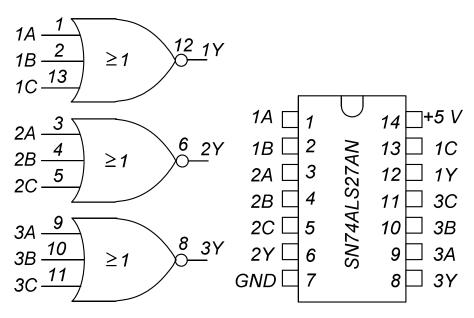

IC KR1533LE4 (SN74ALS27AN) consists of three 3NOR elements. Fig. 1.8 shows its logic diagram and pin configuration. The operation of one section of the IC is described in table 1.10.

Fig. 1.8. IC KR1533LE4 logic diagram and pin configuration

Table 1.10

|    | Inputs    |    | Output |

|----|-----------|----|--------|

| Al | <i>B1</i> | Cl | F1     |

| 0  | 0         | 0  | 1      |

| 0  | 0         | 1  | 0      |

| 0  | 1         | 0  | 0      |

| 0  | 1         | 1  | 0      |

| 1  | 0         | 0  | 0      |

| 1  | 0         | 1  | 0      |

| 1  | 1         | 0  | 0      |

| 1  | 1         | 1  | 0      |

# Truth table for one section of IC KR1533LE4

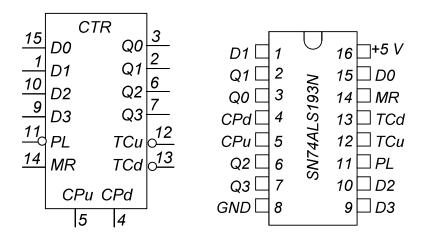

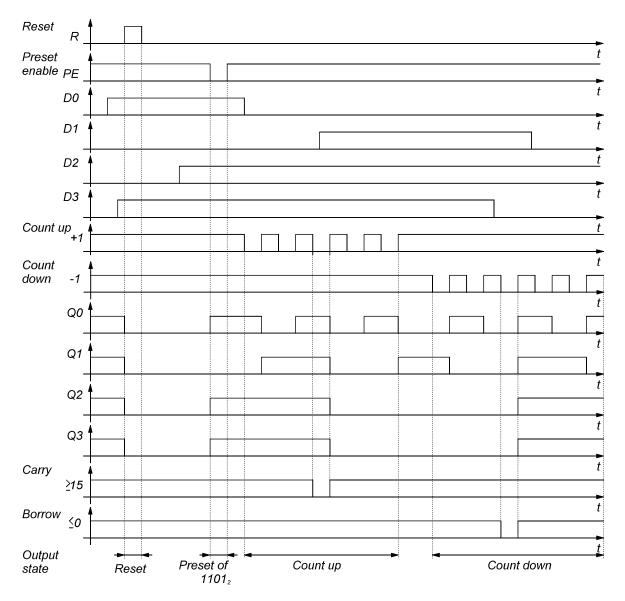

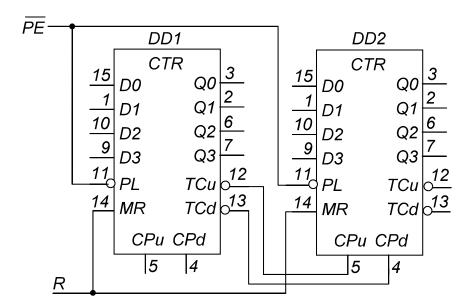

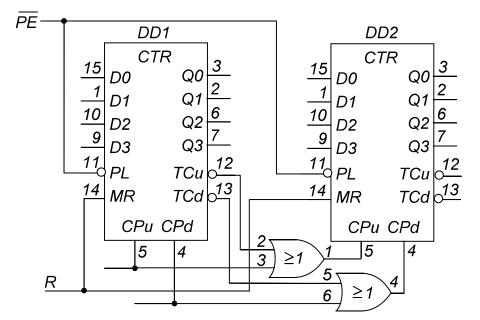

IC KR1533IE7 (SN74ALS193N) is 4-bit up-down counter (will be considered in the Lab work No 7).

### 1.3.4 Examples of BF implementation

### NAND elements based circuit

Fig. 1.9 shows BF circuit implementation (example 1) on the basis of logical elements NAND.

Fig. 1.9. BF implementation on the basis of logical elements NAND

The formation of the variables A, B, C and D is performed via the 4-bit up-down counter KR1533IE7. For this purpose the signals from the built-in frequency divider (embodied into the IC KR1533IE19) or built-in pulse generator output are supplied to the pin +1 of the counter. The number of the

frequency divider output is chosen on account of stable operation of a circuit. For the successful performance of the counter KR1533IE7 input R must be grounded (connected to the common bus).

Fig. 1.10 presents voltage diagrams for the circuit in Fig. 1.9. Table 1.11 shows circuit pins connection to the common point and power supply.

Fig. 1.10. Voltage diagrams for the circuit in Fig. 1.8

Table 1.11

| υ                | U         |           |

|------------------|-----------|-----------|

| Type of IC       | KR1533IE7 | KR1533LA4 |

| Circuitry symbol | DD1       | DD2, DD3  |

| Common           | 8         | 7         |

| + 5 V            | 16        | 14        |

ICs for the circuit in Fig. 1.9

## NOR elements based circuit

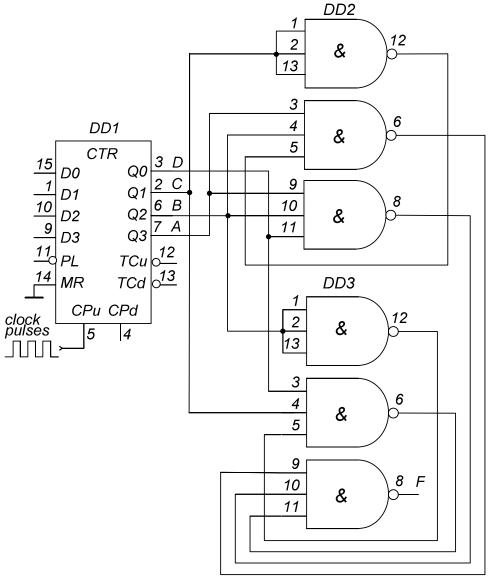

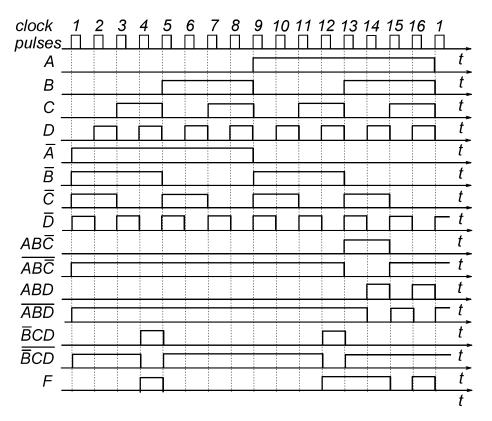

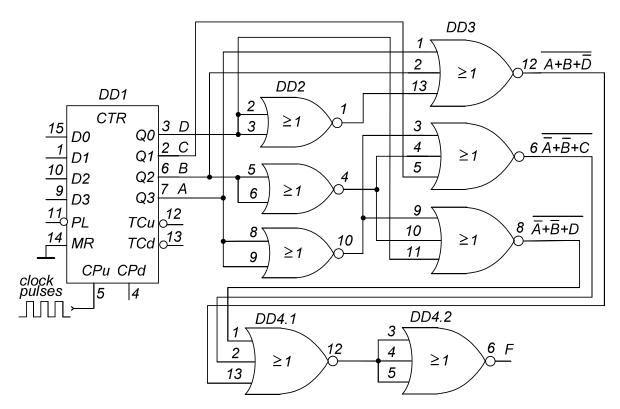

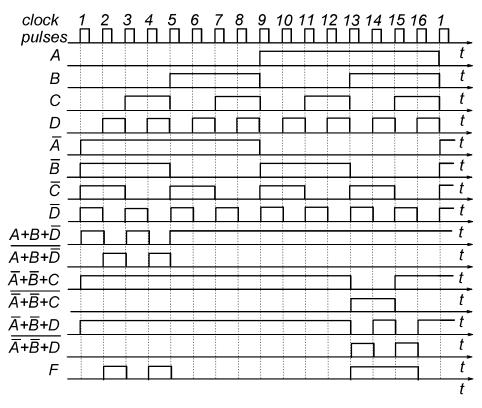

Fig. 1.11 shows BF implementation (example 2) on the basis of logical elements NOR. The formation of the variables A, B, C and D is performed in the same manner as it was described above.

Fig. 1.12 presents voltage diagrams for the given circuit. Table 1.12 shows circuit pins connection to the common bus and power supply.

Fig. 1.11. BF implementation on the basis of logical elements NOR

Fig. 1.12. Voltage diagrams for the circuit in Fig. 1.11

Table 1.12

| Type of IC       | KR1533IE7 | KR1533LE1 | KR1533LE4 |

|------------------|-----------|-----------|-----------|

| Circuitry symbol | DD1       | DD2       | DD3, DD4  |

| Common           | 8         | 7         | 7         |

| + 5 V            | 16        | 14        | 14        |

ICs for the circuit in Fig. 1.11

# **1.4 EQUIPMENT**

In the lab work the module UIK-1 with the relevant software is used. Before starting the work with the module the students are recommended to study carefully its configuration and the software. They are also supposed to understand electronic circuit design principle using the module and the command assignment in the PC application window.

The module is equipped with special ZIF sockets (zero-insertion-force socket) for mounting and fixing microcircuits: 4 sockets for ICs with 14 pins and 4 sockets for IC with 16 pins. To the left and to the right of the connectors we can see a number of plated holes which are connected to the corresponding clips for the IC pins and are intended for oscilloscope probes placing. *Notice*: there are no plated holes for the IC power supply pins (7, 14 or 8, 16).

The module is equipped with a built-in clock pulse generator, frequency divider (on the basis of a binary counter KR1533IE19), seven-segment display, two light-emitting diodes with pull-up resistor, two key buttons connected to the common bus and power supply through a resistor, two 1 k $\Omega$  resistors for setting logic 1 state, and two terminals for interconnecting external devices (generators, oscilloscopes, voltmeters, etc.), which can be added to any part of the circuit.

By default, a built-in generator (integrated circuit SG51P) is not displayed in the program window. It should be added by putting a tick ' $\sqrt{}$ ' in the menu 'Show/Hide circuit elements'. In the menu you can choose what devices built in the module will be displayed on the pinboard.

How to work with the module:

1. Connect the module to the computer via USB-interface.

2. Connect the module to the mains  $\sim$ 220 V. A light-emitting diode will glow green informing that there is power supply of ICs.

3. Open the file *ddevice.lnk* at the Windows desktop and choose "Digital devices" option in the pop-up window.

4. Make sure that the device is ready to work: the sign 'Device is found' appears. If the sign 'Device is not found' or 'Device is preparing'

appears, shut down the programme, switch the module off and repeat steps 1– 3. Sometimes a computer should be reloaded.

5. Insert the IMC into the slots according to the number of pins. Do not embed microcircuits with 14 pins into the slots with 16 clips. Microcircuits must be put into the slots with a key upward. The module has a built-in wiring of the common and power supply buses. Therefore, when the module is on, there is a supply voltage +5 V between left bottom and right upper clips at each socket. **Be careful when mounting microcircuits!**

6. Assemble the required circuit in the program window. When connecting the elements pay attention to the outputs of the IC. They shouldn't be connected together as well as connected to the power supply or common bus.

7. It is highly recommended to save data (button 'Save' at the program command panel) in order not to lose the results of the work.

8. Press the button 'Download data' at the side panel. Only when you push it, the changes made in the circuit are transferred to the module and switching occurs.

To register the waveform and parameters of the output function doublechannel oscilloscope is used.

To fulfil the first laboratory work you'll need a set of simple logic ICs: KR1533LA1, KR1533LA3, KR1533LA4, KR1533LE4, and KR1533LE1 or their analogs. To form the variables *A*, *B*, *C*, *D* binary counter KR1533IE7 is used.

# 1.5 IN-LAB TASKS

1. Connect the counter KR1533IE7. With the help of the built-in divider set minimum clock pulse repetition frequency, make sure that the signals A, B,  $C \bowtie D$  exist.

2. Assemble a NAND circuit at the laboratory bench according to the pre-lab task.

3. Be sure that the logic circuit operation of the given function is correct. Compare the observed waveforms of the functions at the output of the circuit and intermediate points with the pre-lab task results.

4. If there is no coincidence with the results, find the errors which were made while assembling ICs or when simplifying BF. Eliminate the errors and succeed in matching practical and ideal diagrams.

5. Increase clock pulse repetition frequency 4–8 times; compare the diagrams of the circuit operation with the earlier ones. If false function value occurs, find the cause and try to dispose of it.

6. Repeat steps 2–5 for NOR circuit.

# **1.6 QUESTIONS**

1. What does 'irredundant form of the function' mean?

2. Explain the occurrence of critical races on the example of the circuit which you've designed.

3. Draw a truth table for three arguments  $X_1X_2X_3$ , when the function possesses the value 1 if  $X_2$  equals 1. Give Boolean expression for the function having the value 1.

4. How are the ICs with the open collector output connected to each other?

5. What is 'Z-state logic gate'? Give an example.

6. How are outputs of Z-state ICs connected? Give an example.

7. What is usually done with unused inputs of TTL circuits at practice?

8. What is the range of logic 1 level of the gates of CMOS and TTL familys?

9. How can the level of logic 1 (of logic 0) be set at the inputs of TTL/CMOS circuits?

10. When is it possible to connect several outputs of logic gates?

# Lab 2

# MULTIPLEXER STUDY AND CIRCUIT DESIGN ON ITS BASE

# 2.1 OBJECTIVES

The aim of the lab work is to study the functional power of multiplexers in digital devices, and to reinforce skills of performance control of multiplexers in various operational modes during the research work.

#### 2.2 PRE-LAB TASKS

1. Study functional principle, operation modes and pin configuration of ICs KR1533KP2 (SN74ALS153N) and KR1533KP7 (SN74ALS151N).

2. Study the methods of multiplexer capacity increasing.

3. Make clear the fundamental difference between TTL and CMOS multiplexers.

4. Study the implementation principle of logic functions with the help of multiplexers.

5. Design circuits realizing logic functions from the lab work 1 with the use of one IC KR1533KP2, one IC KR1533KP7, two ICs KR1533KP7.

#### 2.3 BASIC THEORY

Multiplexers are digital multi-positional switches. Multiplexers are able to select a definite path of data transmission. Therefore, they are also called data selectors. Sometimes duplicate name is used: 'selector/multiplexer'. Multiplexers vary in the number of data and address inputs, availability of enable inputs and inverted outputs, amount of elements in one IC.

Let us consider ICs KR1533KP7and KR1533KP2. You are offered to analyze their functional power in the lab work.

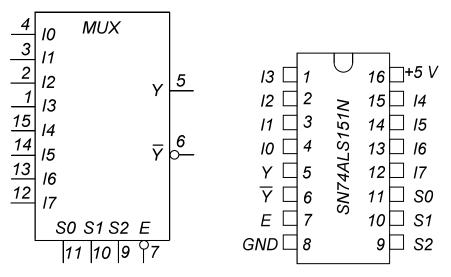

**IC KR1533KP7** is a multiplexer which makes possible to carry data from 8 inputs to one output line, which is presented in a noninverting and inverting format. Fig. 2.1 shows the IC logic symbol and pin configuration.

Fig. 2.1. IC KR1533KP7logic symbol and pin configuration

Logic function, carried out by IC KR1533KP7, is given by (in a noninverting output):

$F = \overline{V}(\overline{A2A1A0D0} + \overline{A2A1A0D1} + \overline{A2A1A0D2} + \dots + A2A1A0D7).$

Table 2.1 characterizes IC KR1533KP7 operation principle.

Table 2.1

|    |    | Inputs |                | (         | Outputs         |

|----|----|--------|----------------|-----------|-----------------|

| A2 | Al | A0     | $\overline{V}$ | F         | $\overline{F}$  |

| Х  | Х  | Х      | 1              | 0         | 1               |

| 0  | 0  | 0      | 0              | $D\theta$ | $\overline{D0}$ |

| 0  | 0  | 1      | 0              | D1        | $\overline{D1}$ |

| 0  | 1  | 0      | 0              | D2        | $\overline{D2}$ |

| 0  | 1  | 1      | 0              | D3        | $\overline{D3}$ |

| 1  | 0  | 0      | 0              | D4        | $\overline{D4}$ |

| 1  | 0  | 1      | 0              | D5        | $\overline{D5}$ |

| 1  | 1  | 0      | 0              | D6        | $\overline{D6}$ |

| 1  | 1  | 1      | 0              | D7        | $\overline{D7}$ |

Multiplexer KR1533KP7 truth table

Digit combination at the address inputs (A2, A1, A0) determines from which data input the signals will be transferred to the outputs in the noninverting format (output 5) and which – in the inverting one (output 6). The enable input  $\overline{V}$  (input 7) must be in a logic 0 state. Logic 1 at the enable input  $\overline{V}$  disables IC operation. In this mode F output is set to a logic 0 state ( $\overline{F}$  output is set to logic 1 state) at any combination of address and data signals.

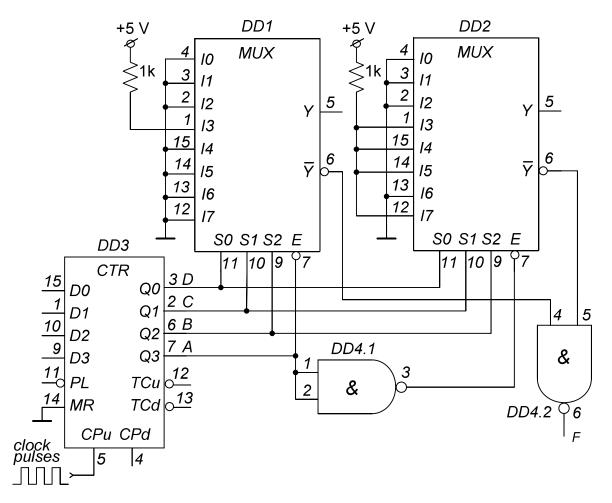

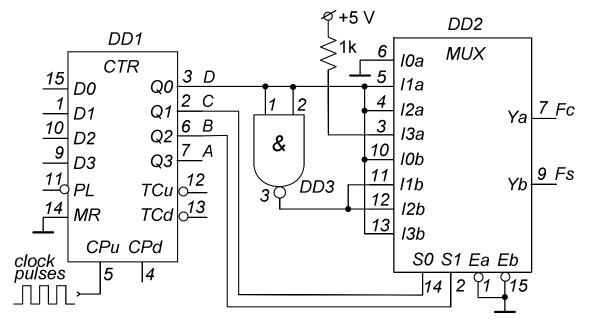

Fig. 2.2 shows BF  $F = \overline{B}CD + ACD + AB\overline{C} + ABD$  implementation circuit on the basis of IC KR1533KP7 (see also table 2.2). In the circuit the most significant variable A lets DD3 and DD4 multiplexers operate one by one. Only half of the truth table values of the function is embodied at each of them (table 1.4), i.e. F = F1 if A = 0, F = F2 if A = 1. Logical summing the variables F1 mu F2 up we obtain the following resulting function F:

$$F = F1 + F2 = \overline{F1} \times \overline{F2}$$

Fig. 2.2. BF implementation on the basis of two ICs KR1533KP7

Table 2.2

| IC type          | KR1533IE7 | KR1533LA3 | KR1533KP7 |  |  |  |  |  |

|------------------|-----------|-----------|-----------|--|--|--|--|--|

| Circuitry symbol | DD1       | DD2       | DD3, DD4  |  |  |  |  |  |

| Common           | 8         | 7         | 8         |  |  |  |  |  |

| + 5 V            | 16        | 14        | 16        |  |  |  |  |  |

*ICs for the circuit in Fig. 2.2*

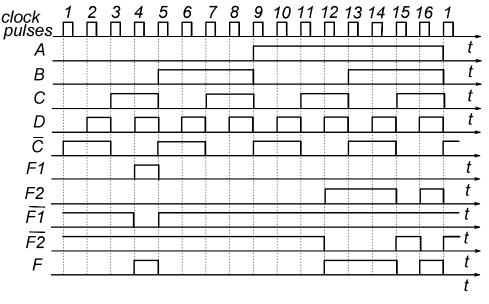

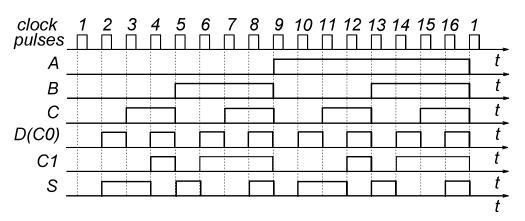

Fig. 2.3 shows voltage diagrams for the circuit presented in Fig. 2.2. Here we can see when multiplexers DD3 (F1) and DD4 (F2) operate. As it follows from the diagrams, the *resulting function* F is the same as in the Lab work 1 (Fig. 1.9).

Fig. 2.3. Voltage diagrams for the circuit in Fig. 2.2

The considered example of BF implementation by means of two multiplexers demonstrates the easiest way of multiplexer digit capacity increase. Lab work 3 will be devoted to the more detailed discussion of the methods of data selectors capacity increase.

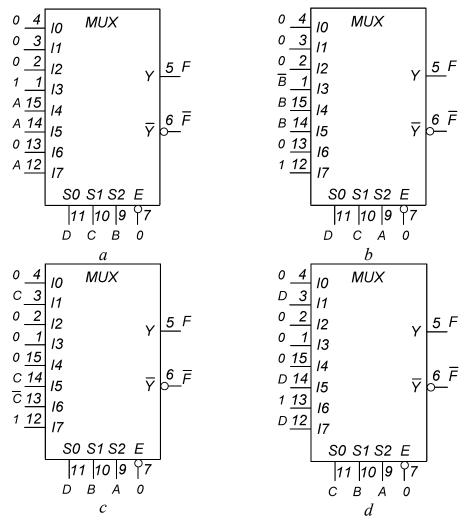

If we want to implement BF by means of one IC KR1533KP7 or KR1533KP2, the given function F should be presented in the table form and linked with one of the four variables: A, B, C or D. Tables 2.3–2.6 and Fig. 2.4 shows how the function F (the values are taken from the lab work 1, see table 1.4) can be linked with various variables and which signals should be fed to the multiplexer inputs in each case. Table 2.3 indicates how it is possible to link the function F and the variable A; table 2.4 – variable B; table 2.5 – variable C; and table 2.6 – variable D.

Fig. 2.5 illustrates the BF implementation method, when the output function is linked with one of the input variables. The circuit is carried into operation by using one IC KR1533KP7. Here the signals formed by the counter KR1533IE7 are used as address variables, and the given function is linked with the variable D (see table 2.6 and Fig. 2.4, d). The application of the given method allows us to reduce the number of multiplexer address inputs by one, i.e. to use microcircuits with the lower number of data inputs.

Table 2.3

| decimal<br>number | В | С | D | A | F |           |

|-------------------|---|---|---|---|---|-----------|

| 0                 | 0 | 0 | 0 | 0 | 0 | 20        |

| 8                 | 0 | 0 | 0 | 1 | 0 | <b>}0</b> |

| 1                 | 0 | 0 | 1 | 0 | 0 | 20        |

| 9                 | 0 | 0 | 1 | 1 | 0 | <b>}0</b> |

| 2                 | 0 | 1 | 0 | 0 | 0 | }0        |

| 10                | 0 | 1 | 0 | 1 | 0 | 30        |

| 3                 | 0 | 1 | 1 | 0 | 1 | }1        |

| 11                | 0 | 1 | 1 | 1 | 1 | 51        |

| 4                 | 1 | 0 | 0 | 0 | 0 | 14        |

| 12                | 1 | 0 | 0 | 1 | 1 | }A        |

| 5                 | 1 | 0 | 1 | 0 | 0 | 14        |

| 13                | 1 | 0 | 1 | 1 | 1 | }A        |

| 6                 | 1 | 1 | 0 | 0 | 0 | }0        |

| 14                | 1 | 1 | 0 | 1 | 0 | 30        |

| 7                 | 1 | 1 | 1 | 0 | 0 | 14        |

| 15                | 1 | 1 | 1 | 1 | 1 | }A        |

Function F linked with variable A

| decimal | В | С | D | A | F |

|---------|---|---|---|---|---|

| number  | D | C | D | А | Γ |

| 0       | 0 | 0 | 0 | 0 | 0 |

| 8       | 0 | 0 | 0 | 1 | 0 |

| 1       | 0 | 0 | 1 | 0 | 0 |

| 9       | 0 | 0 | 1 | 1 | 0 |

| 2       | 0 | 1 | 0 | 0 | 0 |

| 10      | 0 | 1 | 0 | 1 | 0 |

| 3       | 0 | 1 | 1 | 0 | 1 |

| 11      | 0 | 1 | 1 | 1 | 1 |

| 4       | 1 | 0 | 0 | 0 | A |

| 12      | 1 | 0 | 0 | 1 | A |

| 5       | 1 | 0 | 1 | 0 | A |

| 13      | 1 | 0 | 1 | 1 | A |

| 6       | 1 | 1 | 0 | 0 | 0 |

| 14      | 1 | 1 | 0 | 1 | 0 |

| 7       | 1 | 1 | 1 | 0 | A |

| 15      | 1 | 1 | 1 | 1 | A |

Table 2.4

# Function F linked with variable B

| _       |   |   |   |   |   | _          |        |

|---------|---|---|---|---|---|------------|--------|

| decimal | A | С | D | B | F |            |        |

| number  |   |   |   |   |   |            |        |

| 0       | 0 | 0 | 0 | 0 | 0 | 10         |        |

| 4       | 0 | 0 | 0 | 1 | 0 | }0         |        |

| 1       | 0 | 0 | 1 | 0 | 0 | 20         |        |

| 5       | 0 | 0 | 1 | 1 | 0 | }0         |        |

| 2       | 0 | 1 | 0 | 0 | 0 | 20         |        |

| 6       | 0 | 1 | 0 | 1 | 0 | }0         |        |

| 3       | 0 | 1 | 1 | 0 | 1 |            | $\sum$ |

| 7       | 0 | 1 | 1 | 1 | 0 | } <i>B</i> | /      |

| 8       | 1 | 0 | 0 | 0 | 0 | תו         |        |

| 12      | 1 | 0 | 0 | 1 | 1 | } <b>B</b> |        |

| 9       | 1 | 0 | 1 | 0 | 0 | תו         |        |

| 13      | 1 | 0 | 1 | 1 | 1 | } <b>B</b> |        |

| 10      | 1 | 1 | 0 | 0 | 0 | 20         |        |

| 14      | 1 | 1 | 0 | 1 | 0 | <b>}0</b>  |        |

| 11      | 1 | 1 | 1 | 0 | 1 | )1         |        |

| 15      | 1 | 1 | 1 | 1 | 1 | }1         |        |

|           | decimal | A | С | D | В | F              |

|-----------|---------|---|---|---|---|----------------|

|           | number  |   |   |   |   |                |

|           | 0       | 0 | 0 | 0 | 0 | 0              |

|           | 4       | 0 | 0 | 0 | 1 | 0              |

|           | 1       | 0 | 0 | 1 | 0 | 0              |

|           | 5       | 0 | 0 | 1 | 1 | 0              |

|           | 2       | 0 | 1 | 0 | 0 | 0              |

|           | 6       | 0 | 1 | 0 | 1 | 0              |

| $\rangle$ | 3       | 0 | 1 | 1 | 0 | $\overline{B}$ |

|           | 7       | 0 | 1 | 1 | 1 | $\overline{B}$ |

|           | 8       | 1 | 0 | 0 | 0 | B              |

|           | 12      | 1 | 0 | 0 | 1 | B              |

|           | 9       | 1 | 0 | 1 | 0 | B              |

|           | 13      | 1 | 0 | 1 | 1 | B              |

|           | 10      | 1 | 1 | 0 | 0 | 0              |

|           | 14      | 1 | 1 | 0 | 1 | 0              |

|           | 11      | 1 | 1 | 1 | 0 | 1              |

|           | 15      | 1 | 1 | 1 | 1 | 1              |

|           |         |   |   |   |   |                |

| Table 2.5 |

|-----------|

|-----------|

| decimal | A | B | D | С | F |                |

|---------|---|---|---|---|---|----------------|

| number  |   |   |   |   |   |                |

| 0       | 0 | 0 | 0 | 0 | 0 | 20             |

| 2       | 0 | 0 | 0 | 1 | 0 | }0             |

| 1       | 0 | 0 | 1 | 0 | 0 |                |

| 3       | 0 | 0 | 1 | 1 | 1 | } <i>C</i>     |

| 4       | 0 | 1 | 0 | 0 | 0 | 20             |

| 6       | 0 | 1 | 0 | 1 | 0 | <b>}0</b>      |

| 5       | 0 | 1 | 1 | 0 | 0 | 20             |

| 7       | 0 | 1 | 1 | 1 | 0 | <b>}0</b>      |

| 8       | 1 | 0 | 0 | 0 | 0 | 20             |

| 10      | 1 | 0 | 0 | 1 | 0 | <b>}0</b>      |

| 9       | 1 | 0 | 1 | 0 | 0 |                |

| 11      | 1 | 0 | 1 | 1 | 1 | } <i>C</i>     |

| 12      | 1 | 1 | 0 | 0 | 1 |                |

| 14      | 1 | 1 | 0 | 1 | 0 | $\overline{C}$ |

| 13      | 1 | 1 | 1 | 0 | 1 | )1             |

| 15      | 1 | 1 | 1 | 1 | 1 | }1             |

*Function F linked with variable C*

| decimal | A | B | D | C | F              |

|---------|---|---|---|---|----------------|

| number  |   |   |   |   |                |

| 0       | 0 | 0 | 0 | 0 | 0              |

| 2       | 0 | 0 | 0 | 1 | 0              |

| 1       | 0 | 0 | 1 | 0 | С              |

| 3       | 0 | 0 | 1 | 1 | С              |

| 4       | 0 | 1 | 0 | 0 | 0              |

| 6<br>5  | 0 | 1 | 0 | 1 | 0              |

| 5       | 0 | 1 | 1 | 0 | 0              |

| 7       | 0 | 1 | 1 | 1 | 0              |

| 8       | 1 | 0 | 0 | 0 | 0              |

| 10      | 1 | 0 | 0 | 1 | 0              |

| 9       | 1 | 0 | 1 | 0 | С              |

| 11      | 1 | 0 | 1 | 1 | С              |

| 12      | 1 | 1 | 0 | 0 | $\overline{C}$ |

| 14      | 1 | 1 | 0 | 1 |                |

| 13      | 1 | 1 | 1 | 0 | 1              |

| 15      | 1 | 1 | 1 | 1 | 1              |

Table 2.6

# Function F and variable D connection

| decimal | A | B | С | D | F |            |

|---------|---|---|---|---|---|------------|

| number  |   |   |   |   |   |            |

| 0       | 0 | 0 | 0 | 0 | 0 | מר         |

| 1       | 0 | 0 | 0 | 1 | 0 | } <i>0</i> |

| 2       | 0 | 0 | 1 | 0 | 0 | תו         |

| 3       | 0 | 0 | 1 | 1 | 1 | } <b>D</b> |

| 4       | 0 | 1 | 0 | 0 | 0 | מר         |

| 5       | 0 | 1 | 0 | 1 | 0 | } <i>0</i> |

| 6       | 0 | 1 | 1 | 0 | 0 | מר         |

| 7       | 0 | 1 | 1 | 1 | 0 | } <i>0</i> |

| 8       | 1 | 0 | 0 | 0 | 0 | מר         |

| 9       | 1 | 0 | 0 | 1 | 0 | } <i>0</i> |

| 10      | 1 | 0 | 1 | 0 | 0 | תו         |

| 11      | 1 | 0 | 1 | 1 | 1 | } <b>D</b> |

| 12      | 1 | 1 | 0 | 0 | 1 | 11         |

| 13      | 1 | 1 | 0 | 1 | 1 | }1         |

| 14      | 1 | 1 | 1 | 0 | 0 | תו         |

| 15      | 1 | 1 | 1 | 1 | 1 | } <b>D</b> |

|                       | decimal | A | B | С | D | F |

|-----------------------|---------|---|---|---|---|---|

|                       | number  |   |   |   |   |   |

|                       | 0       | 0 | 0 | 0 | 0 | 0 |

|                       | 1       | 0 | 0 | 0 | 1 | 0 |

|                       | 2       | 0 | 0 | 1 | 0 | D |

|                       | 3       | 0 | 0 | 1 | 1 | D |

|                       | 4       | 0 | 1 | 0 | 0 | 0 |

|                       | 5       | 0 | 1 | 0 | 1 | 0 |

| $\mathbf{\mathbf{b}}$ | 6       | 0 | 1 | 1 | 0 | 0 |

| /                     | 7       | 0 | 1 | 1 | 1 | 0 |

|                       | 8       | 1 | 0 | 0 | 0 | 0 |

|                       | 9       | 1 | 0 | 0 | 1 | 0 |

|                       | 10      | 1 | 0 | 1 | 0 | D |

|                       | 11      | 1 | 0 | 1 | 1 | D |

|                       | 12      | 1 | 1 | 0 | 0 | 1 |

|                       | 13      | 1 | 1 | 0 | 1 | 1 |

|                       | 14      | 1 | 1 | 1 | 0 | D |

|                       | 15      | 1 | 1 | 1 | 1 | D |

*Fig. 2.4. BF implementation via linking with the variables A (a), B (b), C (c) and D (d), according to the table 2.3–2.6*

Fig. 2.5. BF implementation by using one IC KR1533KP7 (DD1 – KR1533IE7, DD2 – KR1533KP7)

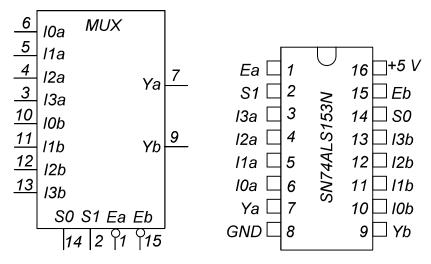

IC KR1533KP2 is a two 4-input multiplexers, having two address inputs A1 and A0, which are common for both multiplexers;  $\overline{V1} \times \overline{V2}$  – enable inputs (active level is low). Two independent outputs transmit the signal levels presented at the multiplexers data inputs selected with the help of the address. Fig. 2.6 shows the IC KR1533KP2 logic symbol and pin configuration.

Fig. 2.6. IC KR1533KP2 logic symbol and pin configuration

The logic function realised by each part of the IC KR1533KP2 has the following form:

$$F = \overline{V}(\overline{A1A0}D0 + \overline{A1}A0D1 + A1\overline{A0}D2 + A1A0D3).$$

The successful operation of the section occurs when the potential of the enable input  $\overline{V}(\overline{VI} \text{ or } \overline{V2})$  is equal to 0.

When  $\overline{V1} = 1$  or  $\overline{V2} = 1$ , the blocking of the corresponded multiplexer section takes place, and logic 0 rate is set at its output despite the data inputs D0-D3 state. The operation of the IC KR1533KP2 is presented in table 2.7.

Table 2.7

|                | Output |    |           |     |     |     |           |

|----------------|--------|----|-----------|-----|-----|-----|-----------|

| $\overline{V}$ | A1     | A0 | $D\theta$ | Dl  | D2  | D3  | F         |

| 0              | 0      | 0  | 1/0       | Х   | Х   | Х   | $D\theta$ |

| 0              | 0      | 1  | Х         | 1/0 | Х   | X   | Dl        |

| 0              | 1      | 0  | Х         | Х   | 1/0 | X   | D2        |

| 0              | 1      | 1  | Х         | Х   | Х   | 1/0 | D3        |

| 1              | Х      | Х  | Х         | Х   | Х   | X   | 0         |

Truth table for KR1533KP2 multiplexer

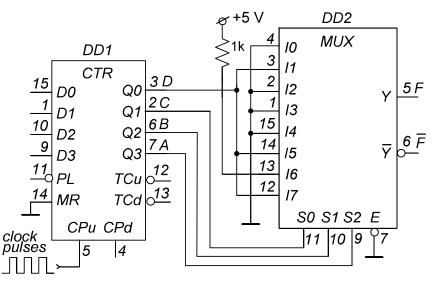

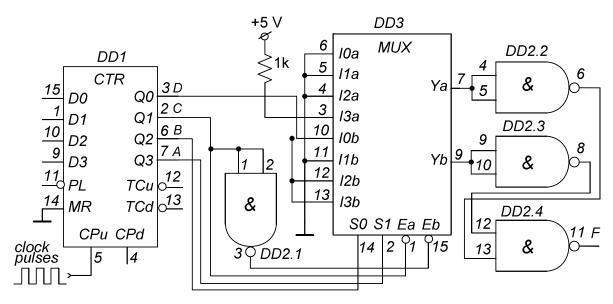

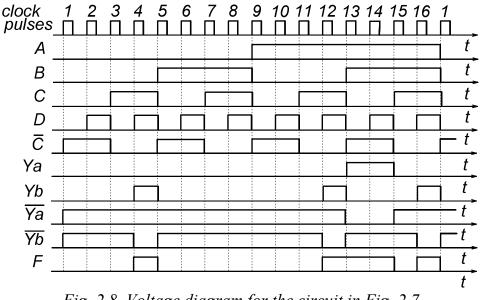

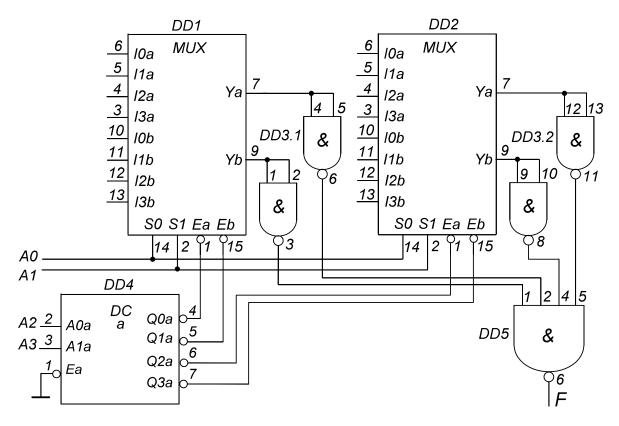

Fig. 2.7 realises the BF  $F = \overline{B}CD + ACD + AB\overline{C} + ABD$ implementation circuit on the basis of IC KR1533KP2 (see also table 2.8), where the prescribed function is linked with the variable *D*. As each part of the multiplexer has only 4 inputs, it is required to increase capacity twice. The signals  $C \ \Bar{C}$  are employed as the signals permitting multiplexer functioning. Thus, to the circuit output the signal takes turns in coming from the multiplexer first and second input, i.e. firstly, from *1D0*, then *2D0*, *1D1*, *2D1*, etc. Fig. 2.8 depicts voltage diagrams in the circuit scheme 2.7 and shows the order of signals selection.

Fig. 2.7. BF implementation by means of IC KR1533KP2

Fig. 2.8. Voltage diagram for the circuit in Fig. 2.7

As you can see from the diagrams (Fig. 2.8), function F is the same as presented in Fig. 2.3 and in the lab work 1 (Fig. 1.9). At the same time the number and mode of intermediate signals is defined by the selected method of the function synthesis.

Table 2.8

| IC type          | KR1533LA3 | KR1533IE7 | KR1533KP2 |

|------------------|-----------|-----------|-----------|

| Circuitry symbol | DD2       | DD1       | DD3       |

| Common           | 7         | 8         | 8         |

| +5 V             | 14        | 16        | 16        |

#### ICs in the circuit in Fig. 2.7

#### 2.4 EQUIPMENT

In the lab work the module UIK-1 with a kit of ICs for 'Digital devices' discipline is used. The procedure of the work is the same as described in section 1.4.

In order to carry out the lab work you'll need a set of microcircuits: KR1533LA3, KR1533KP2, KR1533KP7, KR1533IE7 (to form the variables *A*, *B*, *C* and *D*).

### 2.5 IN-LAB TASKS

1. Check the operating principle of the multiplexer in the steady-state mode. To do this you'll need to provide a random combination of input data to the data and address inputs.

2. Study the functioning of a multiplexer as a converter of a parallel binary code to the serial one. In order to do this you should set the given code to the multiplexer KR1533KP7 data input according to the lecturer's task. The address inputs should be supplied with the counter KR1533IE7 code bit-by-bit. The counter should operate in accumulating mode (+1). Take the waveforms of voltages at the multiplexer inputs and output. Make sure that the code is converted.

3. On the base of one or two KR1533KP7 multiplexers implement the function of 4 variables, which is prescribed in lab work 1 and fulfilled by means of simple logic gates. Be sure that the multiplexer acts as a logical function generator.

4. Implement the function of 4 variables using IC KR1533KP2. Take the waveforms of voltages at the address inputs, enable inputs, multiplexer outputs and whole circuit output.

5. Compare the waveforms from sections  $3 \mu 4$  with the results of the lab work 1. Draw the conclusion.

# 2.6 QUESTIONS

- 1. Why multiplexers are sometimes called selectors? Give the definition of the term 'multiplexer'.

- 2. What are the differences between TTL and CMOS multiplexers? Do they differ in operating principle or functionality?

- 3. What are the differences of TTL family multiplexers?

- 4. What is the output function in the circuit presented in Fig. 2.5 if there is a failure of the pin  $\overline{V1}$  (or  $\overline{V2}$ )?

- 5. What does 'Z-state of a multiplexer' mean?

- 6. Where can multiplexers are applied?

- 7. Explain the multiplexer operating principle.

- 8. Give the definition of the term 'demultiplexer'. Describe its operating principle.

- 9. What are the differences between TTL and CMOS demultiplexers?

- 10. How is it possible to perform the conversion from a parallel binary code to the sequential one?

# Lab 3

# MULTIPLEXER AND DECODER CAPACITY INCREASE. SEVEN-SEGMENT DECODERS STUDY

### **3.1 OBJECTIVES**

The aim of the lab work is to revise the main principles of access devices capacity increase on the basis of multiplexers and decoders. The peculiarities of seven-segment decoder, which is widely used in data display systems, are also studied here.

#### 3.2 PRE-TASKS

1. Study the functional principle, operation modes and pin configuration of the ICs KR1533KP2 (SN74ALS153N), KR1554ID14 (74AC139N) and 533ID18 (SN54LS247), 555ID18 (74LS247N).

2. Study the methods of decoders and multiplexers capacity increase.

3. Get to know the connection circuit of the 7-segment display and the functions described the states of the 7-segment decoder outputs. Write the functions of 4 variables for any three segments.

#### 3.3 BASIC THEORY

The functional principle, logic symbol and the purpose of the IC outputs of the multiplexers (particularly, KR1533KP2 and KR1533KP7) are considered in details in paragraph 2.3. Let us now examine the functional principle of another access device – a decoder.

Decoders (DC – decoder) are the devices used to convert binary input code to the positional output one. At any given time only one of n-outputs is turned on. The selection is performed by means of control signals coming to the proper inputs.

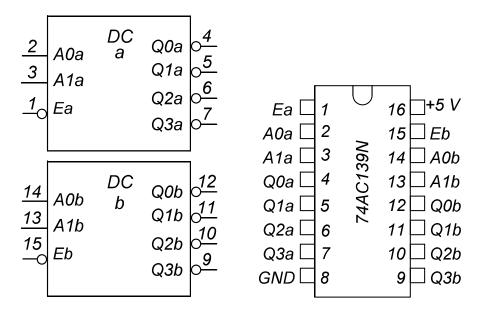

IC KR1554ID14 consists of a pair of two-input decoders. Each of them possesses an enable input and its active state is defined by the low level of the voltage '0'. Decoder's outputs are inverted, i.e. active level also equals '0'. Fig. 3.1 shows the IC KR1554ID14 logic symbol and its pin configuration.

Logic function accomplished by the IC KR1554ID14 is:

$$F0 = X1 + X0 + E0,$$

therefore,

$$F1 = X1 + X0 + E0$$

etc.

Fig. 3.1. IC KR1554ID14 logic symbol and its pin configuration

Table 3.1 represents the operation of one section of the IC KR1554ID14.

Table 3.1

| Input code |    |    | Output state |    |           |    |

|------------|----|----|--------------|----|-----------|----|

| E0         | Xl | XO | F0           | Fl | <i>F2</i> | F3 |

| 0          | 0  | 0  | 0            | 1  | 1         | 1  |

| 0          | 0  | 1  | 1            | 0  | 1         | 1  |

| 0          | 1  | 0  | 1            | 1  | 0         | 1  |

| 0          | 1  | 1  | 1            | 1  | 1         | 0  |

| 1          | Х  | Х  | 1            | 1  | 1         | 1  |

*Truth table for KR1554ID14*

In the lab work the decoder under discussion is going to be used for multiplexer capacity growth. The capacity increase is applied when it is necessary to switch more lines than the given multiplexer allows. The following main methods of multiplexer capacity increase are known.

Cascade multiplexer connection (series connection)

Fig. 3.2 shows the implementation of cascade multiplexer connection. Cascading is performed using 4-input multiplexers.

Fig. 3.2. Cascade multiplexer connection (4-to-1) (DD1, DD2, DD3 – KR1533KP2)

In order to select one out of 16 data inputs it's necessary to have 4 address input lines: A3, A2, A1 and A0. Four basic multiplexers '4-to-1' assure the select according to the code provided to A1 and A0, respectively: the first – one of D0, D1, D2 or D3 signals, the second – D4, D5, D6 or D7 signals, the third – D8, D9, D10 or D11 signals, the fourth –D12, D13, D14 or D15 signals. The fifth multiplexer guarantees the select of one of the formerly selected signals (from the output of the four multiplexers of the first cascade) depending on the code supplied to A3  $\times$  A2. The active input level (in case KR1533KP2 is low) must be supplied to the enable inputs  $\overline{V}$  of all multiplexers. In case of such connection multiplexers without enable input can be used.

Let's define which signal A3A2A1A0 must be provided at the address inputs in order to transmit the signal D10, coming to the input 1D2 of the multiplexer DD2, to the circuit output F1. The input 1D2 corresponds to  $2_{10}$ , therefore, the signal  $10_2$  must be supplied to the address inputs A0A1. In the first cascade of DD1, DD2 multiplexers the signals D2, D6, D10, and D14will be selected. According to the diagram (Fig. 3.2), DD3 multiplexer must connect pin 4 (input 1D2) to the output, where the signal comes from the first section output of DD2 multiplexer. 1D2 input code of DD3 multiplexer equals  $2_{10}$ , thus, the signal  $10_2$  must be supplied to the address inputs A2A3. So, if we want D10 to transmit to the output of the whole circuit, the code  $1010_2$  must occur at address lines A3A2A1A0.

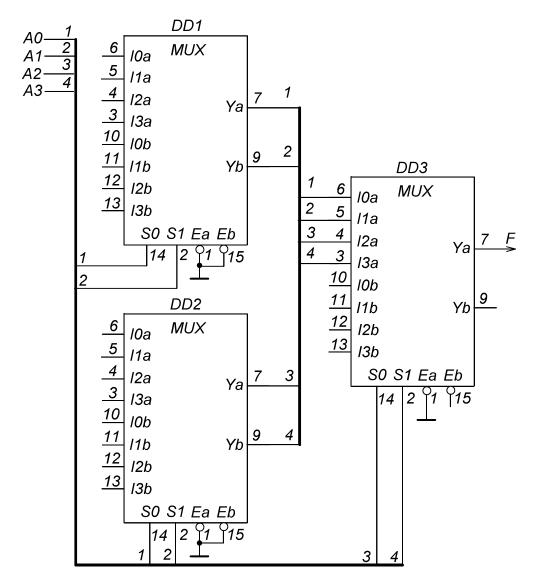

#### Parallel multiplexer connection

Parallel multiplexer connection is realised with the help of a decoder. An illustration of this implementation is shown in Fig. 3.3 (see also table 3.2). In this case the decoder KR1554ID14 is used. To make it work we should supply logic zero to the enable input  $\overline{E0}$ . To select one multiplexer data input out of 16, 4 input address lines: A3, A2, A1  $\mu$  A0 are required. The most significant bits of the addresses A3  $\mu$  A2 are supplied to the decoder data inputs. The corresponding DC outputs are connected to the enable inputs  $\overline{V}$  of the multiplexers (DD2, DD3). DC selects which multiplexer – DD2 or DD3 – will operate. Regardless of the variable D value there will be '0' at the outputs of other multiplexers. In accordance with the code supplied to A1  $\mu$  A0 the active multiplexer selects respectively: the first – one of D0, D1, D2 or D3 signals, the second – D4, D5, D6 or D7 signals, the third – D8, D9, D10 or D11 signals, the fourth – D12, D13, D14 or D15 signals. The signals received from the multiplexer outputs are summed up.

For example, if we supply  $A3A2A1A0 = 0010_2 = 2_{10}$  to the DC data inputs, we'll obtain the code  $A3A2=00_2 = 0_{10}$ , therefore, only the first multiplexer will be allowed to operate. There will be logic 0, i.e. F2=F3=F4=0 at the rest of multiplexers outputs. If a binary code  $A1A0 = 10_2$  $= 2_{10}$  is delivered to all multiplexers address inputs, then the information from 1D2 input (i.e. the value of the variable D2) will be transferred to the F1DD2 output. After being summed, F=F1+F2+F3+F4 = 0 + 0 + 0 + D2 = D2will be at the output of the whole circuit.

*Fig. 3.3. The circuit of multiplexer capacity increase with the help of a decoder*

Table 3.2

IC in the circuit in Fig. 3.3

| IC type          | KR1533KP2 | KR1554ID14 | KR1533LA3 | KR1533LA1 |

|------------------|-----------|------------|-----------|-----------|

| Circuitry symbol | DD1, DD2  | DD4        | DD3       | DD5       |

| Common           | 8         | 8          | 7         | 7         |

| +5 V             | 16        | 16         | 14        | 14        |

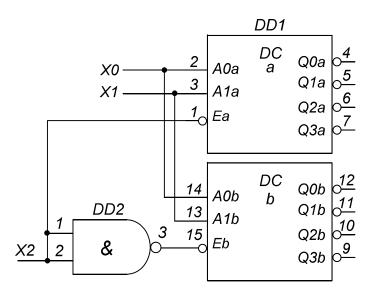

#### Decoder capacity increase

It is often necessary to provide an access to devices which amount exceeds the digit capacity of given decoder. The enable input allows us to increase the decoder capacity. Fig. 3.4 shows the simplest scheme of decoder capacity increase up to 8 outputs on the basic of dual 4-output decoder KR1554ID14 and an inverter. The least significant bits X1X0 of the X2X1X0 input code are supplied to the similar data inputs of both decoders, high-order bit X2 – to the enable input. Moreover, one of the decoders is supplied with inverted X2 signal. Depending on the variable X2 value, only one section of KR1554ID14 will function. At the same time, there are inactive signals at all the outputs of the second section. The operation of the decoder capacity increase circuit is presented in table 3.4.

Fig. 3.4. Decoder capacity increase circuit on the IC KR1554ID14 basis (DD1 – KR1554ID14, DD2 – KR1533LA3)

| Table 3.4 | • |

|-----------|---|

|-----------|---|

|    | Inputs |    | Outputs |           |           |    |           |           |           |           |

|----|--------|----|---------|-----------|-----------|----|-----------|-----------|-----------|-----------|

| X2 | Xl     | XO | FO      | <i>F1</i> | <i>F2</i> | F3 | <i>F4</i> | <i>F5</i> | <i>F6</i> | <i>F7</i> |

| 0  | 0      | 0  | 0       | 1         | 1         | 1  | 1         | 1         | 1         | 1         |

| 0  | 0      | 1  | 1       | 0         | 1         | 1  | 1         | 1         | 1         | 1         |

| 0  | 1      | 0  | 1       | 1         | 0         | 1  | 1         | 1         | 1         | 1         |

| 0  | 1      | 1  | 1       | 1         | 1         | 0  | 1         | 1         | 1         | 1         |

| 1  | 0      | 0  | 1       | 1         | 1         | 1  | 0         | 1         | 1         | 1         |

| 1  | 0      | 1  | 1       | 1         | 1         | 1  | 1         | 0         | 1         | 1         |

| 1  | 1      | 0  | 1       | 1         | 1         | 1  | 1         | 1         | 0         | 1         |

| 1  | 1      | 1  | 1       | 1         | 1         | 1  | 1         | 1         | 1         | 0         |

Decoder capacity increase (Fig. 3.4)

Decoder capacity can be enhanced by analogy with the parallel method of multiplexer capacity increase (Fig. 3.3). For example, if it is necessary to implement a 16-output decoder, you'll need five 4-output decoders with enable inputs. In this case the first decoder – DC1 (high-order bits of the input code are supplied to its inputs) selects which decoder DC2–DC5 will function. Therefore, the signals from DC1 outputs are connected to DC2– DC5 enable inputs, and data inputs of the same name D0 and D1 are joined together and connected to the least significant bits of the input code.

#### Seven-segment decoder study

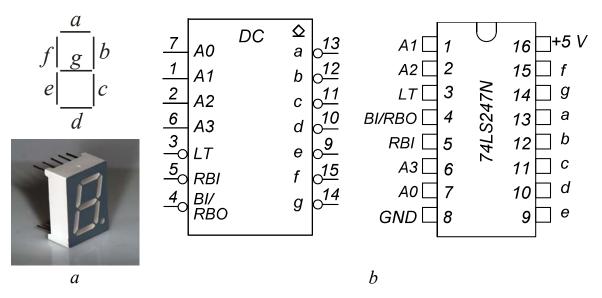

7-segment decoders are applied for converting binary code to the 7segment one. 7-segment code is essential for displaying figures from 0 to 9 at a digital indicator. The code is called 7-segment because the figures are depicted in the form of the so called 'segments' (Fig. 3.5, a). The display often has one more additional segment – a dot. Actually, 7-segment decoders are the elements with the open collector (inverted output) or an open emitter (non- inverted output). Along with such decoders the displays with common anodes or cathodes are used.

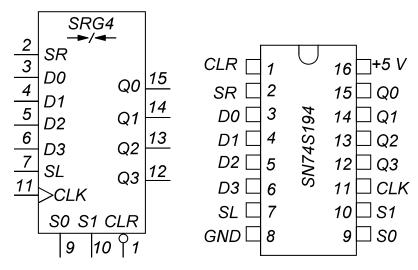

In the lab work the 7-segment decoder 533ID18 (SN54LS247) (555ID18 (74LS247N) is also possible) with open collector outputs is used. Fig. 3.5 shows the IC 533ID18 logic symbol and pin configuration.

IC 533ID18 is a decoder-driver for converting binary-decimal code to the 7-segment one. It is designed for operating with the common anode indicator, which is connected to the outputs a-g (active low level). The inputs X0-X3 are supplied with a number in a binary code. Being excited by a lowlevel signal, the lighting test input (LT) makes the outputs a - g active. When the same excitation signal is supplied to the blanking input (B1), high level appears at all outputs, and causes the previous test values of the indicator to be reset. Successive blanking input (RB1) is intended for IC 533ID18 operation composed of multidigit display. When RB1 input is excited by a low-level signal, the indicator blanking takes place only if zero is currently displayed. When the input RB1 becomes active, for some time the output B1/RB0 becomes the output of the successive blanking signal (RB0) and the high-level signal is changed by the low-level signal. It should be noted here that 'blanking' means emission cease of all indicator LEDs.

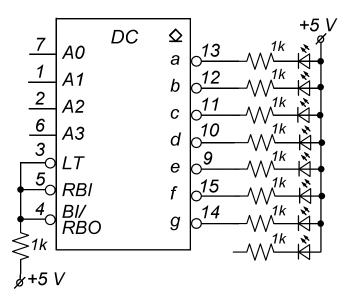

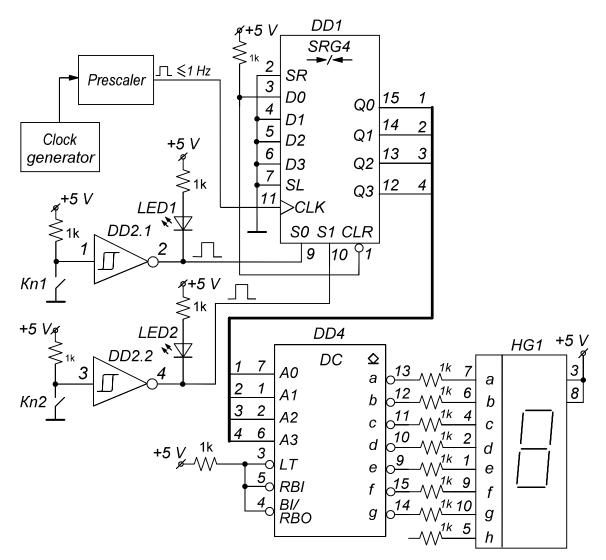

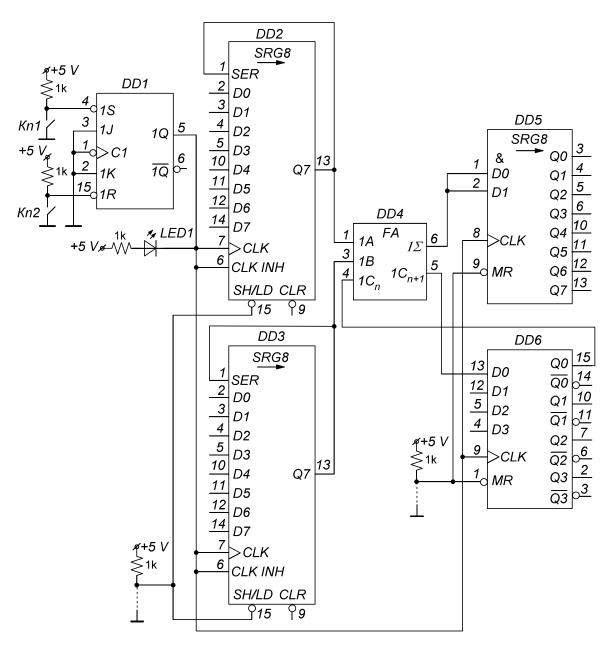

Fig. 3.6 presents the connection circuit of the 7-segment display with a common anode to the decoder 533ID18. The display SA04-12 from 'Kingbright' is used in our lab work.

Fig. 3.5. Exterior view of a seven-segment display (a), the IC 533ID18 logic symbol and pin configuration (b)

*Fig. 3.6. Connection circuit of the 7-segment display to the decoder 533ID18 (555ID18)*

| Tał | ole | 3.5 |

|-----|-----|-----|

|-----|-----|-----|

| Decimal<br>numbers/ | Input code |     |    |    |    |    | <i>B1/</i> | Outputs |   |   |   |   |   |   |

|---------------------|------------|-----|----|----|----|----|------------|---------|---|---|---|---|---|---|

| functionality       |            |     |    |    |    |    | RB0        |         |   |   |   |   |   |   |

| dec                 | LT         | RB1 | X3 | X2 | Xl | XO |            | a       | b | С | d | е | f | G |

| 0                   | 1          | 1   | 0  | 0  | 0  | 0  | 1          | 0       | 0 | 0 | 0 | 0 | 0 | 1 |

| 1                   | 1          | X   | 0  | 0  | 0  | 1  | 1          | 1       | 0 | 0 | 1 | 1 | 1 | 1 |

| 2                   | 1          | Х   | 0  | 0  | 1  | 0  | 1          | 0       | 0 | 1 | 0 | 0 | 1 | 0 |

| 3                   | 1          | Х   | 0  | 0  | 1  | 1  | 1          | 0       | 0 | 0 | 0 | 1 | 1 | 0 |

| 4                   | 1          | Х   | 0  | 1  | 0  | 0  | 1          | 1       | 0 | 0 | 1 | 1 | 0 | 0 |

| 5                   | 1          | X   | 0  | 1  | 0  | 1  | 1          | 0       | 1 | 0 | 0 | 1 | 0 | 0 |

| 6                   | 1          | X   | 0  | 1  | 1  | 0  | 1          | 1       | 1 | 0 | 0 | 0 | 0 | 0 |

| 7                   | 1          | Х   | 0  | 1  | 1  | 1  | 1          | 0       | 0 | 0 | 1 | 1 | 1 | 1 |

| 8                   | 1          | Х   | 1  | 0  | 0  | 0  | 1          | 0       | 0 | 0 | 0 | 0 | 0 | 0 |

| 9                   | 1          | Х   | 1  | 0  | 0  | 1  | 1          | 0       | 0 | 0 | 0 | 1 | 0 | 0 |

| 10                  | 1          | X   | 1  | 0  | 1  | 0  | 1          | 1       | 1 | 1 | 0 | 0 | 1 | 0 |

| 11                  | 1          | Х   | 1  | 0  | 1  | 1  | 1          | 1       | 1 | 0 | 0 | 1 | 1 | 0 |

| 12                  | 1          | Х   | 1  | 1  | 0  | 0  | 1          | 1       | 0 | 1 | 1 | 1 | 0 | 0 |

| 13                  | 1          | Х   | 1  | 1  | 0  | 1  | 1          | 0       | 1 | 1 | 0 | 1 | 0 | 0 |

| 14                  | 1          | X   | 1  | 1  | 1  | 0  | 1          | 1       | 1 | 1 | 0 | 0 | 0 | 0 |

| 15                  | 1          | Х   | 1  | 1  | 1  | 1  | 1          | 1       | 1 | 1 | 1 | 1 | 1 | 1 |

| <i>B1</i>           | X          | Х   | X  | X  | X  | Х  | 0          | 1       | 1 | 1 | 1 | 1 | 1 | 1 |

| RB1                 | 1          | 0   | 0  | 0  | 0  | 0  | 0          | 1       | 1 | 1 | 1 | 1 | 1 | 1 |

| LT                  | 0          | Х   | Х  | Х  | Х  | Х  | 1          | 0       | 0 | 0 | 0 | 0 | 0 | 0 |

Truth table for the decoder 533ID18

Table 3.5 represents the operation of the decoder. *Notice:*

• For lines 0–15: when it is desirable to display numbers from 0 to 15, the blanking input *B1* must be disconnected or have high logic level signal. The successive blanking input *RB1* must be disconnected or have high logic level, if decimal zero suppression is unwanted.

• For line *B1*: when low-level voltage comes directly to the blanking input *B1*, all segment outputs are turned off without regard to the level of any other input.

• For line *RB1*: when the voltage at the input *RB1* and the voltage at the inputs X0-X3 bear low level, and the voltage is high at the *LT*, all segment outputs are turned off and the level *RB0* becomes low (trigger condition).

• For line LT: when the blanking input/output of the successive blanking (*B1/RB0*) is disconnected or bears high voltage level, and the input LT is provided with low voltage, all segment outputs are turned on.

• Symbol 'x' means non-operating inputs.

It should be noted that the signals at the input corresponded to the decimal numbers 10, 11, 12, 13, 14 and 15 make specific signals appear at the decoder 533ID18 outputs. These signals relate to the incomplete digital images at the display.

### 3.4 EQUIPMENT

In the lab work the ICs of the multiplexer KR1533KP2 and decoders KR1554ID14 and 533ID18 are studied. The laboratory bench has a built-in 7-segment display with pull-down resistors. The wires connection points are marked with the letters a - g for segments and h – point. The implementation of the required connections of the ICs is performed at the pinboard of the module UIK-1 with the assistance of ordinary equipment: an oscilloscope, and a personal computer.

### 3.5 IN-LAB TASKS

1. Increase multiplexer KR1533KP2 capacity by cascade connection (Fig. 3.2) and check if the circuit functions correctly by setting up the address given by the lecturer and by supplying a random pulse sequence to the proper input of one of the multiplexers.

2. Implement a logic function of 4 variables. The function which was discussed earlier in the lab works 1 and 2 is used. As a source of logic variables the counter KR1533IE7, which operates in the accumulating mode (+1), is employed. Take the waveforms of signals at the multiplexer output and address inputs.

3. Increase multiplexer KR1533KP2 capacity by parallel connection (Fig. 3.3) and check if the circuit functions correctly by setting up the address given by the lecturer and by supplying a random pulse sequence to the proper input of one of the multiplexers.

4. Implement a logic function of 4 variables by means of parallel connection. Compare the results achieved in paragraph 2 and previous lab works. Make a conclusion.

5. Verify the operating principle of the decoder KR1554ID14 in a static mode. To fulfil this task you should supply the code (given by the lecturer) to the data inputs.

6. Implement decoder capacity increase up to 8 using the circuit in Fig. 3.4. Check the circuit performance by supplying alternating binary code as *X3X2X1* signals. The code is formed by means of the counter KR1533IE7.

7. Display the given number at the built-in 7-segment display by connecting the proper inputs to the power supply or zero potential.

8. Connect the decoder 533ID18 to the 7-segment display. According to the lecturer's task set the given number on the display (Fig. 3.6).

9. Study how the decoder functions if the input code is more than 9. Make a conclusion.

## 3.6. QUESTIONS

- 1. Design a multiplexer 16-to-1 on the basis of the multiplexer KR1533KP7. Present a circuit in the lab work report.

- 2. Design a multiplexer 16-to-1 on the basis of the multiplexer KR1533KP2. Present a circuit in the lab work report.

- 3. Think of case studies of multiplexing. What is it applied for?

- 4. Give a definition of 'a decoder'. Describe its operating principle, and show the truth table. Speak about the application of decoders.

- 5. Is it possible to increase the decoder capacity if the decoders without enable input are used? How?

- 6. Describe a 7-segment display, its types and circuits.

- 7. Explain what a 7-segment code is and how is it formed?

- 8. Implement 8-output decoder capacity increase in order to obtain a 16output decoder.

- 9. How is it possible to implement a 4-output demultiplexer on the basis of DC KR1554ID14.

- 10. Design a circuit of 8-bit demultiplexer on the basis of DC KR1554ID14 and basic logic gates.

## Lab 4

# CIRCUIT DESIGN AND STUDY OF HALF-ADDER AND FULL-ADDER ON THE BASIS OF MULTIPLEXERS AND LOGIC GATES

### 4.1 OBJECTIVES

The lab work acquaints students with the execution of arithmetic operations on binary numbers, on the one hand, and the implementation of elementary arithmetic units using multiplexers and simple logic gates, on the other hand.

#### 4.2 PRE-TASKS

- 1. In terms of one-digit binary numbers addition be able to make up truth tables for a half-adder and a half-subtracter. Write down the equations.

- 2. Draw a half-adder circuit in NAND basis.

- 3. Study the half-adder/half-subtracter operating principle (Fig. 4.2) and logic structure.

- 4. Draw the diagrams of a half-adder and a half-subtracter operation.

- 5. Study the operating principle of one-digit and two-digit adders.

- 6. On the base of the table 4.10 construct the circuit for the one-digit subtracter using the IC KR1533KP2.

### 4.3 BASIC THEORY

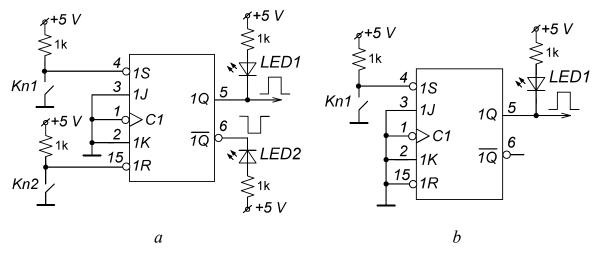

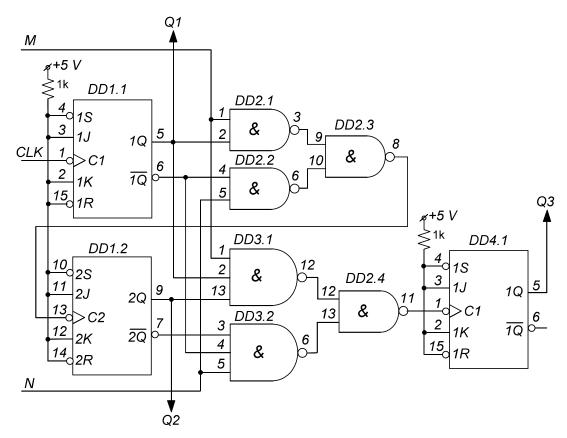

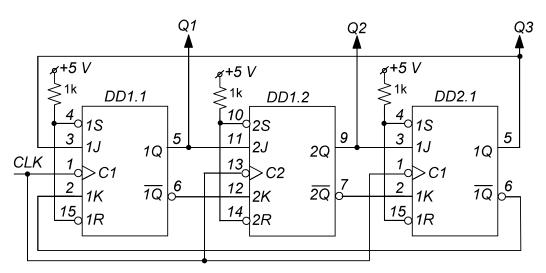

In the lab work elementary arithmetic units are analysed. Their peculiarity lies in the fact that the signals are attributed arithmetic values 0 and 1, but not logic ones, and the operations made on them follow the binary arithmetic laws. The lab work is devoted to the design and study of the half-adder circuits based on the simple logic IC KR1533LA3, KR1533LP5, one-digit and two-digit adders and one-digit subtracter on the basis of IC KR1533KP2 multiplexer.

Adders are the electronic assemblies performing binary numbers addition. The adders are divided into two groups according to the mode of operation: combinational – having no memory elements and storage adders – those which store the results of previous calculations. Depending on the number processing technique each adder in its turn can be classified as series or parallel. Both of them are built on the basis of single-digit adding circuits. Therefore, in the lab work the fundamentals of the elementary half-adder circuit, single-digit full-adder and full-subtracter design are considered.

The addition of numbers in series adders is fulfilled bit-by-bit, step-bystep. In parallel adders all digits of multidigited numbers are added simultaneously.

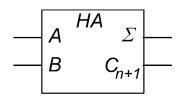

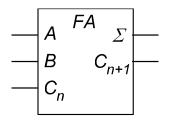

The simplest adding element is a half-adder shown in Fig. 4.1. There are two inputs A and B for the summands and two outputs: S (sum)  $\mu$  C (carry) here. The half-adder can be used only if we need to add two single-digit numbers. Table 4.1 presents the combination logic device operating principle.

Fig. 4.1. Half-adder

Table 4.1

| Truth table for a half-adder |  |   |   |   |  |  |  |  |

|------------------------------|--|---|---|---|--|--|--|--|

| A                            |  | В | S | С |  |  |  |  |

| Α | В | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

The sum *S* and carry *C* output functions can be defined in the following way:

$$S = \overline{AB} + A\overline{B},$$

$$C = AB.$$

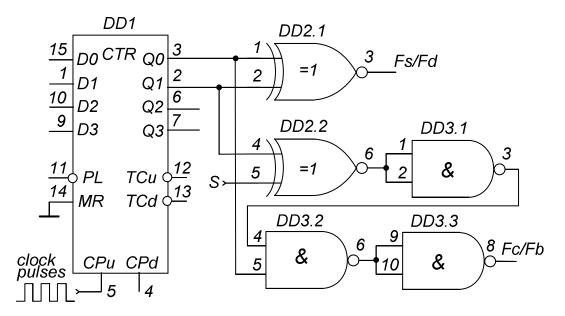

The implementation of the universal half-adder/half-subtracter based on the logic gates KR1533LP5 (SN74ALS86N) – 'EXCLUSIVE OR', is shown in Fig. 4.2 (see also table 4.2). When summed up the outputs correspond to *Fs*  $\mu$  *Fc* (sum and carry, respectively), when subtracted – *Fd*  $\mu$  *Fb* (difference and borrow). Table 4.3 presents the circuit functioning. A pair of adjacent variables from the counter output is used as input variables.

Table 4.2

| IC type          | KR1533IE7 | KR1533LP5 | KR1533LA3 |  |  |  |  |  |  |

|------------------|-----------|-----------|-----------|--|--|--|--|--|--|

| Circuitry symbol | DD1       | DD2       | DD3       |  |  |  |  |  |  |

| Common           | 8         | 7         | 7         |  |  |  |  |  |  |

| +5 V             | 16        | 14        | 14        |  |  |  |  |  |  |

ICs of the circuit in Fig. 4.2

Fig. 4.2. Half-adder/half-subtracter circuit

Table 4.3

| 7 | <i>Truth table for the circuit in Fig. 4.2</i> |    |    |       |       |  |  |  |  |  |  |

|---|------------------------------------------------|----|----|-------|-------|--|--|--|--|--|--|

| S | Operation                                      | Xl | X0 | Fs/Fd | Fc/Fb |  |  |  |  |  |  |

| 0 |                                                | 0  | 0  | 0     | 0     |  |  |  |  |  |  |

| 0 | }subtraction                                   | 0  | 1  | 1     | 1     |  |  |  |  |  |  |

| 0 |                                                | 1  | 0  | 1     | 0     |  |  |  |  |  |  |

| 0 |                                                | 1  | 1  | 0     | 0     |  |  |  |  |  |  |

| 1 |                                                | 0  | 0  | 0     | 0     |  |  |  |  |  |  |

| 1 | }addition                                      | 0  | 1  | 1     | 0     |  |  |  |  |  |  |

| 1 |                                                | 1  | 0  | 1     | 0     |  |  |  |  |  |  |

| 1 |                                                | 1  | 1  | 0     | 1     |  |  |  |  |  |  |

Single-digit full-adder is shown in Fig. 4.3. There are three inputs: A and B for the summands and  $C_0$  for the carry from the lower bit addition, and two outputs: S (sum) and C (carry). The sum S and carry C output functions can be defined in the following manner:

> $S = \overline{ABC_0} + \overline{ABC_0} + \overline{ABC_0} + \overline{ABP_0} = (A \oplus B)\overline{C_0} + \overline{(A \oplus B)C_0},$  $P = \overline{ABC_0} + A\overline{BC_0} + AB\overline{C_0} + AB\overline{C_0} = AB + (A \oplus B)C_0.$

Fig. 4.3. Full-adder

Table 4.4 describes full single-digit adder functioning.

Table 4.4

| i ani iubie jor a jan aaae |   |       |   |   |  |  |  |  |  |

|----------------------------|---|-------|---|---|--|--|--|--|--|

| Α                          | В | $C_0$ | S | С |  |  |  |  |  |

| 0                          | 0 | 0     | 0 | 0 |  |  |  |  |  |

| 0                          | 0 | 1     | 1 | 0 |  |  |  |  |  |

| 0                          | 1 | 0     | 1 | 0 |  |  |  |  |  |

| 0                          | 1 | 1     | 0 | 1 |  |  |  |  |  |

| 1                          | 0 | 0     | 1 | 0 |  |  |  |  |  |

| 1                          | 0 | 1     | 0 | 1 |  |  |  |  |  |

| 1                          | 1 | 0     | 0 | 1 |  |  |  |  |  |

| 1                          | 1 | 1     | 1 | 1 |  |  |  |  |  |

*Truth table for a full-adder*

In the lab work it is required to implement a single-digit adder circuit on the basis of the multiplexer KR1533KP2. To perform the task you need 'to bind' the sum S and carry C functions with one of the IC KR1533IE7 output variables B, C or D. Table 4.5 illustrates full single-digit adder output function obtained by binding to the variable D, where S – the sum of the variables B, C  $\mu$  D=C<sub>0</sub>, and C<sub>1</sub> – carry to the next digit by adding variables B, C and C<sub>0</sub>.

Table 4.5

| В | } | С | D | $C_0$ | S | $C_1$ | $C_1 \begin{array}{c} \text{Data inputs} \\ \text{KR1533KP2} (S) \end{array}$ |                |     | Data inputs<br>KR1533KP2 (C <sub>1</sub> ) |  |

|---|---|---|---|-------|---|-------|-------------------------------------------------------------------------------|----------------|-----|--------------------------------------------|--|

| 0 | ) | 0 | 0 | 0     | 0 | 0     | 2D0                                                                           | Π              | 1D0 | 0                                          |  |

| 0 | ) | 0 | 1 | 1     | 1 | 0     | 2D0                                                                           | D              | ID0 | 0                                          |  |

| 0 | ) | 1 | 0 | 0     | 1 | 0     | 2D1                                                                           | <u>_</u>       | 1D1 | ת                                          |  |

| 0 | ) | 1 | 1 | 1     | 0 | 1     | 2DI                                                                           | D              | IDI | D                                          |  |

| 1 |   | 0 | 0 | 0     | 1 | 0     | 2D2                                                                           | $\overline{D}$ | 1D2 | ת                                          |  |

| 1 |   | 0 | 1 | 1     | 0 | 1     | 2D2                                                                           | D              | ID2 | D                                          |  |

| 1 |   | 1 | 0 | 0     | 0 | 1     | 2D3                                                                           | Π              | 1D3 | 1                                          |  |

| 1 |   | 1 | 1 | 1     | 1 | 1     | 2D5                                                                           | D              | 1D5 | 1                                          |  |

Binding between the full-adder output functions and the variable D

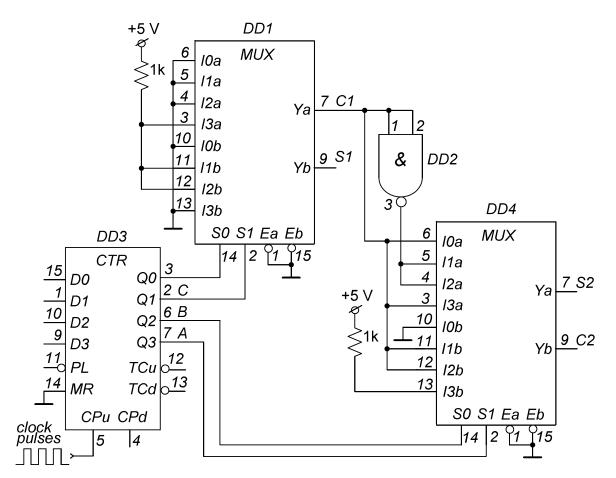

Table 4.5 also shows what signals should be supplied to the IC KR1533KP2 data inputs (see the right four columns) in order to put a full single-digit adder into operation. At the same time the operation of both multiplexer sections must be permitted ( $\overline{V1} = \overline{V2} = 0$ ). Fig. 4.4 depicts single-digit adder circuit on the basis of the IC KR1533KP2 (see also table 4.6). Figure 4.5 shows voltage diagrams for the given circuit.

Fig. 4.4. Single-digit adder on the IC KR1533KP2 basis

Fig. 4.5. Voltage diagrams for the circuit in Fig. 4.4

Table 4.6

| ICs for the circuit in Fig. 4.4 |           |           |           |  |  |  |  |  |  |

|---------------------------------|-----------|-----------|-----------|--|--|--|--|--|--|

| IC type                         | KR1533IE7 | KR1533KP2 | KR1533LA3 |  |  |  |  |  |  |

| Circuitry symbol DD1 DD2 DD3    |           |           |           |  |  |  |  |  |  |

| Common 8 8 7                    |           |           |           |  |  |  |  |  |  |

| +5 V 16 16 14                   |           |           |           |  |  |  |  |  |  |

In the lab work it is also necessary to implement a two-digit adder circuit (the truth table is shown in table 4.7) on the basis of the same multiplexer KR1533KP2, where S1 is the sum of the variables C and D (low-order bits); C1 – the carry to the next digit by adding the variables C and D; S2 – the sum of the variables A, B (high-order bits) and C1; C2 – the carry to the next digit by adding the variables how to perform

the binding of the sum S2 and carry C2 with the variable C1. Table 4.8 shows what signals should be supplied (see columns S1, C1, S2  $\mu$  C2) to the IC KR1533KP2 data inputs in order to implement a two-digit adder.

Fig. 4.6 depicts the two-digit adder circuit on the IC KR1533KP2 basis (see also table 4.9). Fig. 4.7 shows voltage diagrams for the given circuit.

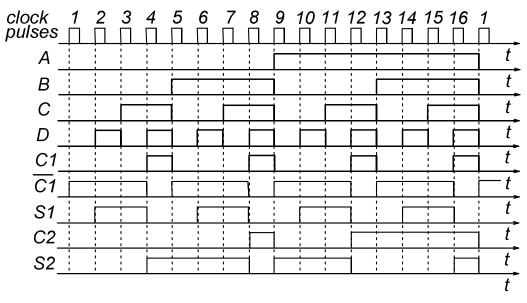

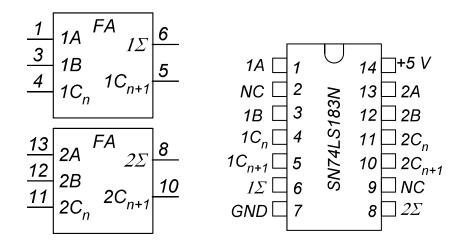

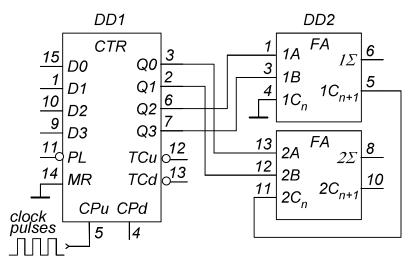

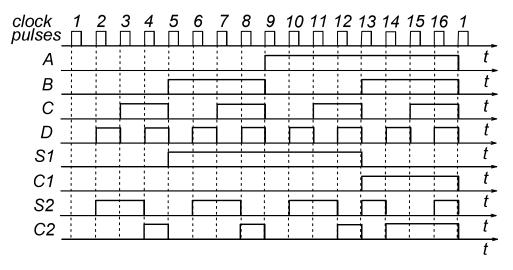

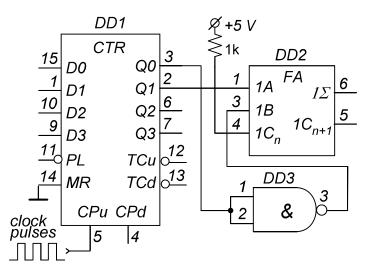

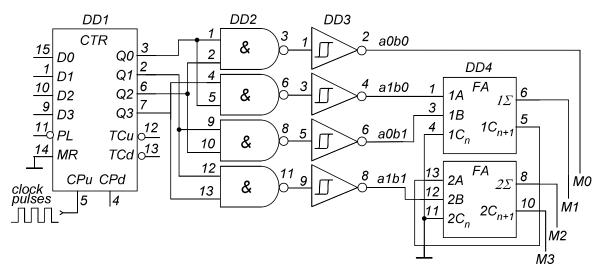

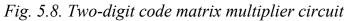

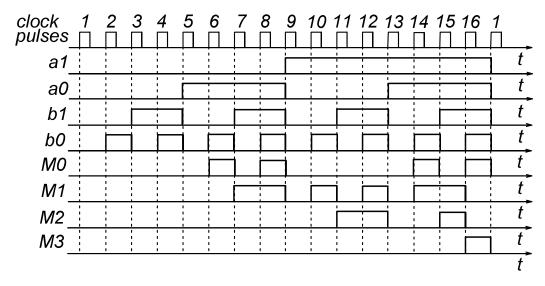

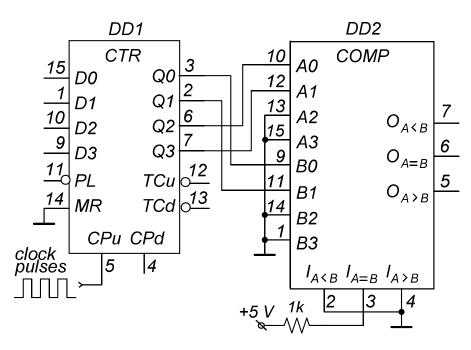

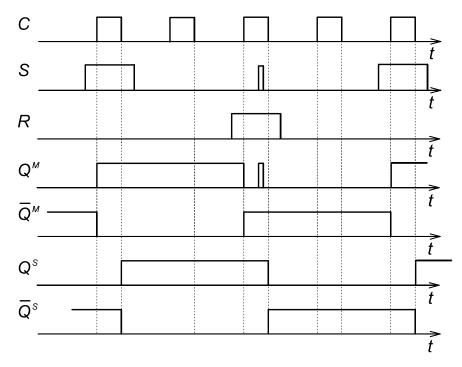

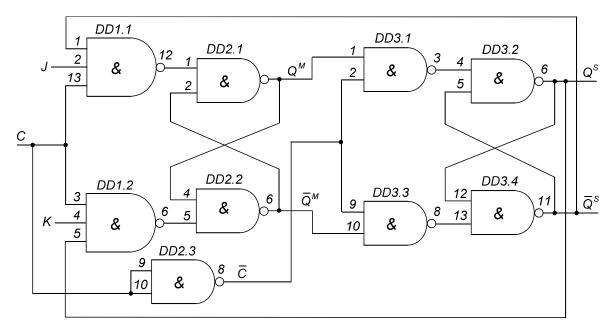

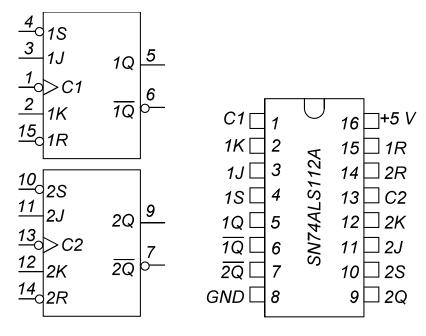

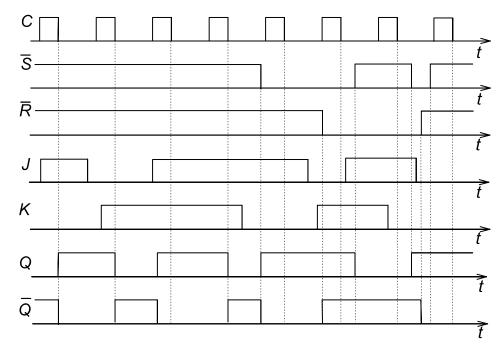

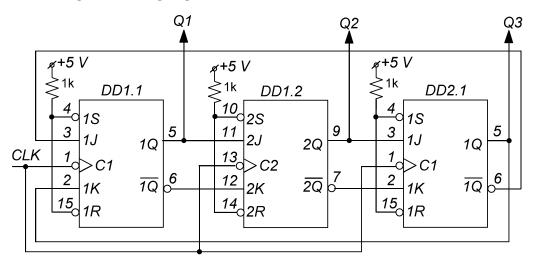

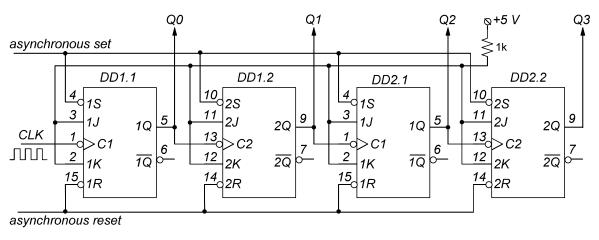

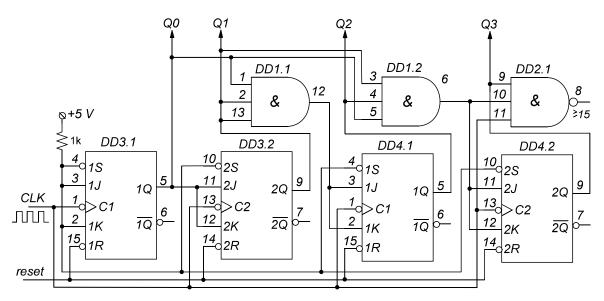

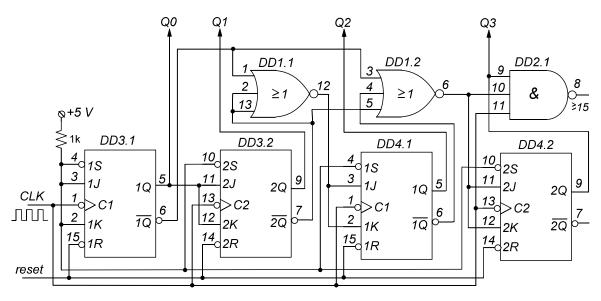

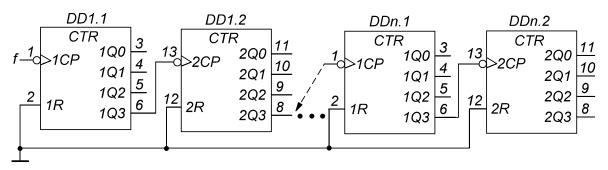

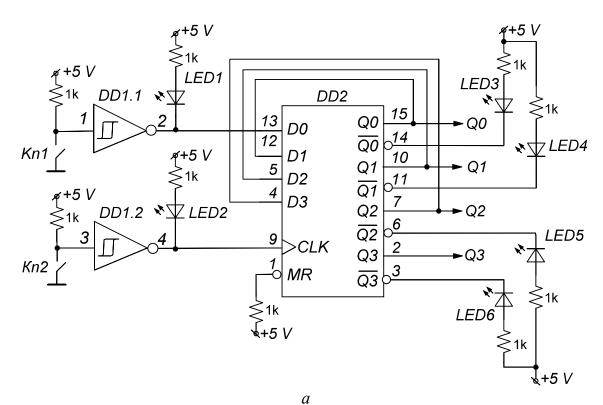

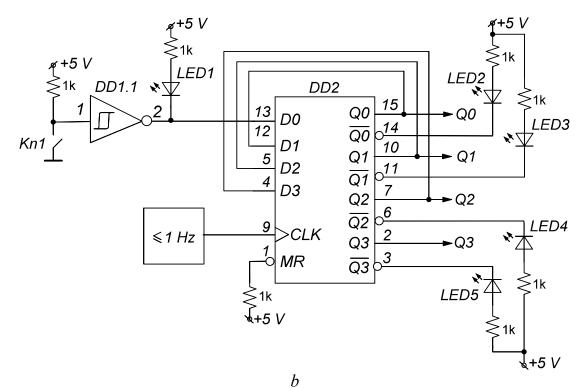

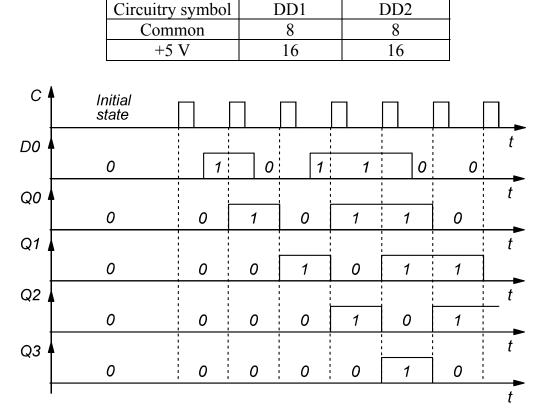

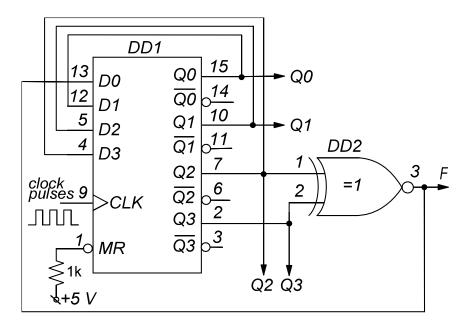

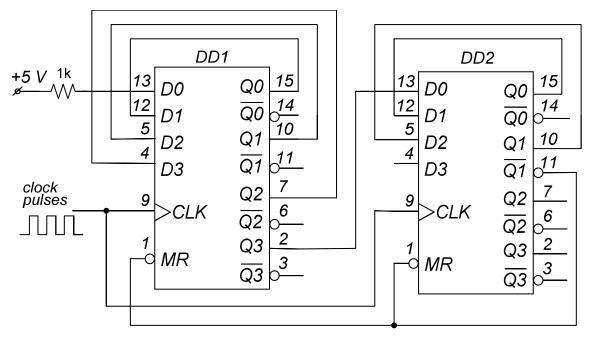

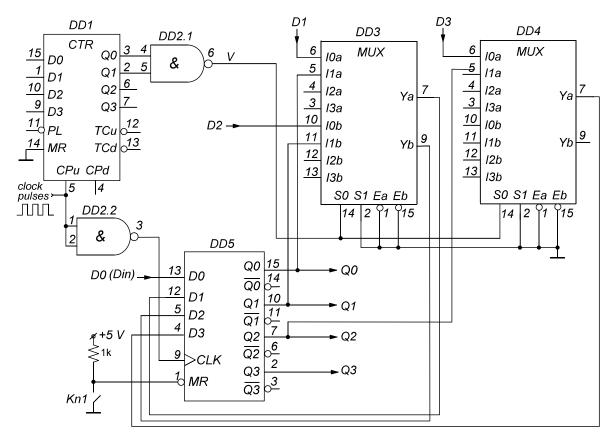

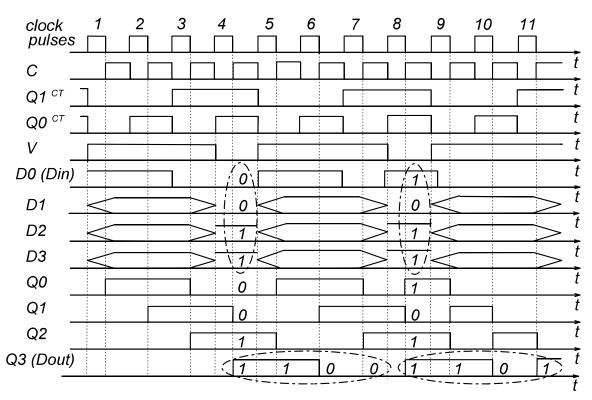

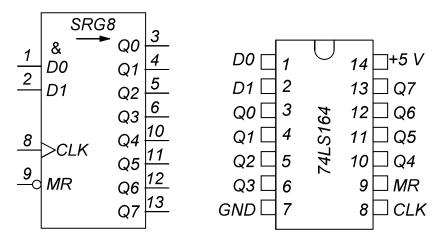

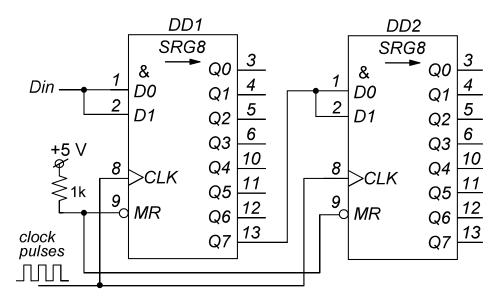

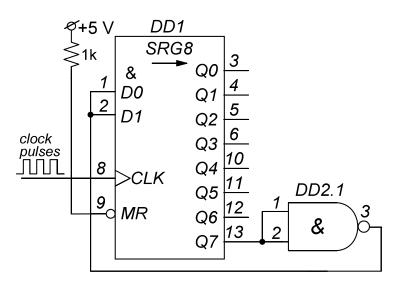

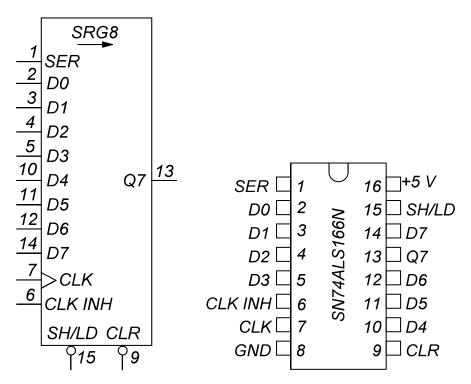

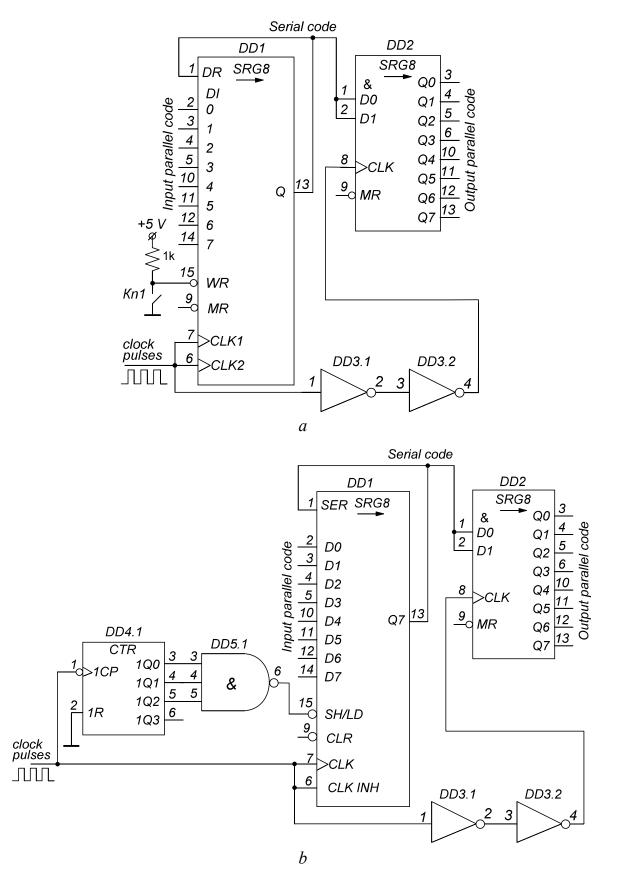

Table 4.7