# Цифровые устройства

# Содержание курса

- 1. Базовые логические элементы

- а) основы булевой алгебры

- б) базовые логические элементы

- 2. Комбинационные логические устройства

- а) мультиплексоры

- б) демультиплексоры и дешифраторы

- в) шифраторы

- г) арифметические устройства

- 3. Логические устройства последовательного типа

- а) триггеры

- б) счетчики

- в) регистры

- 4. АЦП и ЦАП

- 5. Запоминающие устройства

# Цифровые устройства

## Рейтинг - план

| № п/п | Наименование деятельности         | Рейтинг |

|-------|-----------------------------------|---------|

| 1     | Обязательные виды работ:          | 60      |

| 1.1   | выполнение ИДЗ (2 х 12 баллов)    | 24      |

| 1.2   | выполнение лаб. работ (6 х 6)     | 36      |

| 2     | Дополнительные виды работ:        | 40      |

| 2.1   | контрольные работы (4 х 8 баллов) | 32      |

| 2.2   | доп. лаб. работа (1 х 8)          | 8       |

|       | Допуск к экзамену                 | 40      |

# Литература

- 1. Якубовский С.В. Цифровые и аналоговые интегральные микросхемы. М.: Радио и связь. 1990.

- 2. Токхейм Р. Основы цифровой электроники. Пер. с англ. М.: Мир, 1988. 390 с.

- 3. Шило В.Л. Популярные цифровые микросхемы. М.: Радио и связь, 1990. –350 с.

- 4. Бирюков С.А. Цифровые устройства на МОП-интегральных микросхемах М.: Радио и связь. 1992 (1996).

- 5. Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника. Полный курс: учебник для вузов. М.: Горячая линия, 1999 (2000, 2005). 768 с.

- 6. Алексенко А.В., Шагуров И.И. Микросхемотехника. М.: Радио и связь, 1990 (1982).

- 7. Большие интегральные схемы ЗУ./ Под ред. А.Ю. Гордонова, Ю.Н. Дьякова. Справочное пособие. М: Радио и связь, 1990. 286 с.

- 8. Федорков Б.Г., Телец В.А. Микросхемы ЦАП и АЦП: Функционирование, параметры, применение. М.: Энергоатомиздат, 1990. 320 с.

- 9. Гилмор Ч. Введение в микропроцессорную технику. Пер. с англ. М.: Мир, 1984.

- 10. Пухальский С.А. Проектирование дискретных устройств на интегральных микросхемах. 1990.

- 11. Микросхемы АЦП и ЦАП : справочник. М. : Додэка-XXI, 2005. 431 с. : ил.

- 12. <a href="http://www.qrz.ru">http://www.qrz.ru</a>

- 13. <a href="http://www.cqham.ru">http://www.cqham.ru</a>

- 14. <a href="http://ru.wikipedia.org">http://ru.wikipedia.org</a>

- 15. <a href="http://naf-st.ru">http://naf-st.ru</a>

#### Системы счисления

#### непозиционные

#### позиционные

$$X = X_{n-1}q^{n-1} + X_{n-2}q^{n-2} + ... + x_0q^0 + X_{-1}q^{-1} + ... + X_{-m}q^{-m},$$

где q - основание системы счисления,  $X_i$  – разрядный коэффициент  $(X_i = 0...q$ -1), q i – весовой коэффициент.

Двоичная система счисления - q = 2 (два цифровых знака 0 и 1)

## Электронное устройство имеет два состояния.

в цепи протекает ток / в цепи нет тока, напряжение положительное / напряжение отрицательное, цепь замкнута / цепь разомкнута

Для математического моделирования цифровых систем вводятся **логические переменные**, которые принимают значения x=0 и x=1. **Логические функции** переводят одни логические переменные в другие логические переменные.

Раздел математики, описывающий соотношения между различными логическими переменными и функциями, называется *булевой алгеброй* (или *алгеброй логики*).

**Функция** алгебры логики (или булева функция) - зависимость выходных переменных yi, выраженная через совокупность входных переменных xn-1...x1x0 с помощью операций алгебры логики.

Булевы функции (БФ) могут быть *одной переменной* y = f(x0), *двух* y = f(x0,x1) и более переменных y = f(x1,x2,x3...xn), где y, x1,x2,x3...xn могут принимать только значения 0 и 1.

**Таблица истинности функции** (или элемента, реализующего эту функцию) – это таблица, содержащая все возможные комбинации входных логических переменных и соответствующие им значения логической функции.

# 1. Логическое отрицание (инверсия) – функция **НЕ**:

| X | y |

|---|---|

| 0 | 1 |

| 1 | 0 |

$$y = \overline{x}$$

# 2. Логическое сложение (дизъюнкция) – функция ИЛИ:

| $\mathbf{x}_0$ | $\mathbf{x}_1$ | у |

|----------------|----------------|---|

| 0              | 0              | 0 |

| 1              | 0              | 1 |

| 0              | 1              | 1 |

| 1              | 1              | 1 |

$$y=x_0+x_1$$

или  $y=x_0\vee x_1$

# 3. Логическое умножение (конъюнкция) – функция И

| $\mathbf{x}_0$ | $\mathbf{x}_1$ | y |

|----------------|----------------|---|

| 0              | 0              | 0 |

| 1              | 0              | 0 |

| 0              | 1              | 0 |

| 1              | 1              | 1 |

$$y = x_0 x_1$$

$$y = x_0 \cdot x_1$$

$$y = x_0 \wedge x_1$$

$$y = x_0 \& x_1$$

# 4. Функция неравнозначности:

| $\mathbf{x}_0$ | $\mathbf{x}_1$ | У |

|----------------|----------------|---|

| 0              | 0              | 0 |

| 1              | 0              | 1 |

| 0              | 1              | 1 |

| 1              | 1              | 0 |

$$y = (\overline{x_0} \wedge x_1) \vee (x_0 \wedge \overline{x_1})$$

ИЛИ

$$y = x_0 \oplus x_1$$

### 5. Функция равнозначности:

| $\mathbf{x}_0$ | $\mathbf{x}_1$ | y |

|----------------|----------------|---|

| 0              | 0              | 1 |

| 1              | 0              | 0 |

| 0              | 1              | 0 |

| 1              | 1              | 1 |

$$y = (x_0 \wedge x_1) \vee (\overline{x_0} \wedge \overline{x_1})$$

ИЛИ

$$y = \overline{x_0 \oplus x_1}$$

## Функция Пирса

$$y = x_0 \vee x_1$$

## Правило повторения

$$x \wedge x = x$$

$$x \lor x = x$$

## Теорема Де-Моргана

$$\frac{x_0 \wedge x_1 = x_0 \vee x_1}{x_0 \vee x_1} = \frac{x_0 \vee x_1}{x_0 \wedge x_1}$$

## Функция Шиффера

$$y = x_0 \wedge x_1$$

### Правило отрицания

$$x \wedge x = 0$$

$$x \vee \overline{x} = 1$$

#### Тождества

$$x \wedge 1 = x$$

$x \wedge 0 = 0$

$$x \lor 1 = 1$$

$x \lor 0 = x$

# Переместительный закон

$$x_0 \cdot x_1 = x_1 \cdot x_0$$

$$x_0 + x_1 = x_1 + x_0$$

# Распределительный закон

$$(x_0 \cdot x_1) + (x_0 \cdot x_2) = x_0 \cdot (x_1 + x_2)$$

$$(x_0 + x_1) \cdot (x_0 + x_2) = x_0 + (x_1 \cdot x_2)$$

#### Сочетательный закон

$$(x_0 \cdot x_1) \cdot x_2 = x_0 \cdot (x_1 \cdot x_2) = x_0 \cdot x_1 \cdot x_2$$

$$(x_0 + x_1) + x_2 = x_0 + (x_1 + x_2) = x_0 + x_1 + x_2$$

# Формы представления логических функций

#### 1. Словесное описание $\mathcal{F}\Phi$

Пример 1. Логическая функция трех переменных равна единице, если хотя бы две входные переменные равны единице.

### 2. Описание БФ в виде таблицы истинности

**Паблицай** остажетиний оступистицили ти дком бинациюнной таблицей Рещенны табинца, меодержащая бее и возможные комбинации

входных переменных хг выходных переменных

В общем случае таблица столбцов.

| X  | v     | v     | v     |   | ачения |

|----|-------|-------|-------|---|--------|

|    | $x_2$ | $x_1$ | $x_0$ | У |        |

| ļά | 0     | 0     | 0     | 0 | и n+m  |

|    | 0     | 0     | 1     | 0 |        |

|    | 0     | 1     | 0     | 0 |        |

|    | 0     | 1     | 1     | 1 |        |

|    | 1     | 0     | 0     | 0 |        |

|    | 1     | 0     | 1     | 1 |        |

|    | 1     | 1     | 0     | 1 |        |

|    | 1     | 1     | 1     | 1 | 11     |

## 3. Описание ФАЛ в виде алгебраического выражения

Используются две стандартные формы БФ:

**Дизъюнктивной нормальной формой** (ДНФ) называется логическая сумма элементарных логических произведений, в каждое из которых аргумент или его инверсия входит один раз.

ДНФ записывается по таблице истинности с использованием следующего алгоритма:

- а) для каждого набора переменных, на котором БФ равна единице, записывают элементарные логические произведения входных переменных, причем переменные, равные нулю, записывают с инверсией. Полученные произведения называют конституентами единицы;

- б) логически суммируют все конституенты единицы.

**Совершенной ДНФ** называется форма записи, когда в каждом слагаемом присутствуют все переменные.

12

# 3. Описание ФАЛ в виде алгебраического выражения

Используются две стандартные формы БФ:

**Конъюнктивной нормальной формой** (КНФ) называется логическое произведение элементарных логических сумм, в каждую из которых аргумент или его инверсия входят 1 раз.

КНФ записывается по таблице истинности с использованием следующего алгоритма:

- а) для каждого набора переменных, для которого БФ равна нулю, записывают элементарные логические суммы входных переменных, причем переменные, значения которых равны единице, записывают с инверсией. Полученные суммы называют конституентами нуля;

- б) логически перемножают все полученные конституенты нуля.

**Совершенной КНФ** называется форма записи, когда в каждом множителе присутствуют все переменные.

**Пример 3.** Записать ДНФ для БФ, заданной в примере 2. *Решение.* Согласно приведенному алгоритму (по единицам) получим:

| $x_2$ | $x_1$ | $x_0$ | y |

|-------|-------|-------|---|

| 0     | 0     | 0     | 0 |

| 0     | 0     | 1     | 0 |

| 0     | 1     | 0     | 0 |

| 0     | 1     | 1     | 1 |

| 1     | 0     | 0     | 0 |

| 1     | 0     | 1     | 1 |

| 1     | 1     | 0     | 1 |

| 1     | 1     | 1     | 1 |

$$y(x_2, x_1, x_0) = \overline{x_2} x_1 x_0 + x_2 \overline{x_1} x_0 + x_2 \overline{x_1} x_0 + x_2 \overline{x_1} x_0 + x_2 \overline{x_1} x_0$$

**Пример 4.** Записать КНФ для БФ, заданной в примере 2. *Решение.* Применяя вышеприведенный алгоритм (по нулям), получим

$$y(x_{2}, x_{1}, x_{0}) = (x_{2} + x_{1} + x_{0}) \cdot (x_{2} + x_{1} + x_{0})$$

$$\cdot (x_{2} + x_{1} + x_{0}) \cdot (x_{2} + x_{1} + x_{0})$$

<sub>14</sub>

# 4. Описание ФАЛ в виде последовательности десятичных чисел

Иногда для сокращения записи БФ представляют в виде последовательности десятичных чисел. При этом последовательно записывают десятичные эквиваленты двоичных кодов соответствующих конституент единицы или нуля.

**Пример 7.** Записать в виде последовательности чисел БФ из примеров 3 и 4. *Решение*. В ДНФ из примера 3 первая конституента «единица»  $(x_2x_1x_0)$  соответствует двоичному коду 011. Десятичный эквивалент этого кода равен 3. Аналогично записываются все остальные конституенты:

$$y(x_{2}, x_{1}, x_{0}) = x_{2}x_{1}x_{0} + x_{2}x_{1}x_{0} + x_{2}x_{1}x_{0} + x_{2}x_{1}x_{0}$$

$$y(x_{2}, x_{1}, x_{0}) = \sum_{i=0}^{\infty} (3, 5, 6, 7)$$

$$y(x_{2}, x_{1}, x_{0}) = (x_{2} + x_{1} + x_{0}) \cdot (x_{2} + x_{1} + \overline{x_{0}}) \cdot (x_{2} + \overline{x_{1}} + x_{0}) \cdot (\overline{x_{2}} + x_{1} + x_{0})$$

$$y(x_{2}, x_{1}, x_{0}) = \prod_{i=0}^{\infty} (0, 1, 2, 4)$$

<sub>15</sub>

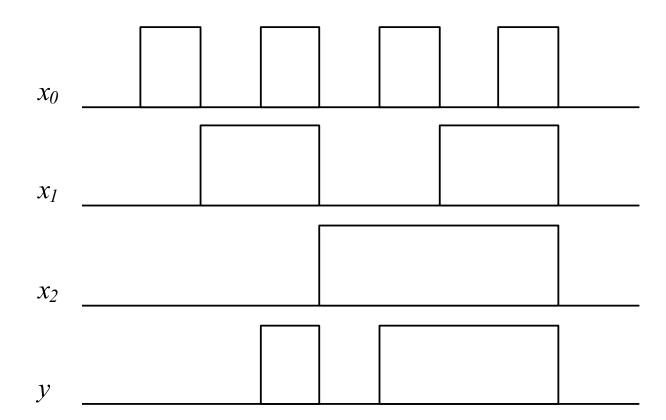

# 5. Графическое представление БФ

а) представление в виде последовательности импульсов

б) кубические комплексы (самостоятельно)

# Методы минимизации логических функций

*Определение*: Преобразование логических функций с целью упрощения их аналитического представления называется **минимизацией**.

#### Направления минимизации:

- **1.Кратчайшая форма записи** (цель минимизировать ранг каждого терма). При этом получаются кратчайшие формы КДНФ, ККНФ.

- **2.Получение минимальной формы записи** (цель получение минимального числа символов для записи всей функции сразу).

#### Методы минимизации:

#### 1. Метод непосредственных преобразований логических функций.

При применении данного метода:

- а) Записываются СДНФ логической функции

- б) Форма преобразуется и упрощается с использованием операций алгебры логики.

- **2. Метод минимизирующих карт** карты Карно (Вейча), Удобны для небольшого числа переменных.

# -

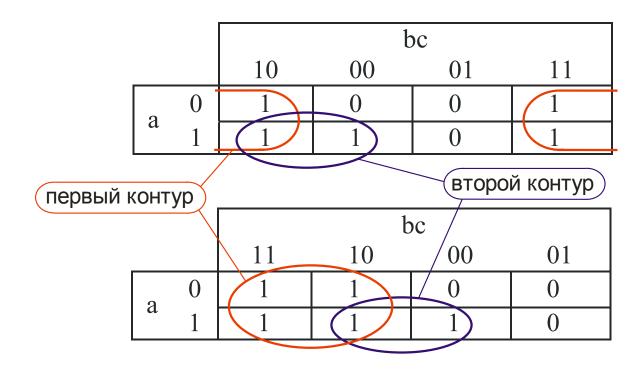

# Карта Карно

Карта Карно – графическое представление таблицы истинности.

Каждой клетке карты Карно соответствует строка таблицы истинности. По осям карты расставляются сочетания переменных, а внутри карты — значения функции. *Назначение карты Карно* — найти логические суммы прямого и инверсного значения переменных.

Для любой переменной, например a, такая сумма равна  $a + \bar{a} = 1$  при любом значении a: при a = 0 это будет 0+1=1, при a=1 это 1+0=1.

Поэтому при вынесении за скобки в выражении

$$abc + \overline{abc} = bc(a + \overline{a}) = bc \cdot 1 = bc$$

#### Правила разметки осей карты:

- 1. Вертикальная ось размечается независимо от горизонтальной.

- 2. Начинать разметку можно с любого сочетания переменных.

- 3. Все сочетания переменных должны быть перечислены.

- 4. Для соседних клеток карты сочетание переменных должно отличаться не более чем одним знаком, причем соседними являются крайние клетки строки (столбца).

# Таблица истинности и карта Карно для функции двух переменных

| a | b | f(a,b) |

|---|---|--------|

| 0 | 0 | f(0,0) |

| 0 | 1 | f(0,1) |

| 1 | 0 | f(1,0) |

| 1 | 1 | f(1,1) |

|   |   | b      |        |

|---|---|--------|--------|

|   |   | 1 0    |        |

|   | 0 | f(0,1) | f(0,0) |

| a | 1 | f(1,1) | f(1,0) |

Для функции двух переменных карта Карно — это квадрат 2х2 клетки.

# Таблица истинности и карта Карно для функции трех переменных

| a | b | c | f(a,b,c) |

|---|---|---|----------|

| 0 | 0 | 0 | f(0,0,0) |

| 0 | 0 | 1 | f(0,0,1) |

| 0 | 1 | 0 | f(0,1,0) |

| 0 | 1 | 1 | f(0,1,1) |

| 1 | 0 | 0 | f(1,0,0) |

| 1 | 0 | 1 | f(1,0,1) |

| 1 | 1 | 0 | f(1,1,0) |

| 1 | 1 | 1 | f(1,1,1) |

|    |    | С        |          |  |

|----|----|----------|----------|--|

|    |    | 1        | 0        |  |

|    | 00 | f(0,0,1) | f(0,0,0) |  |

| ab | 01 | f(0,1,1) | f(0,1,0) |  |

| au | 11 | f(1,1,1) | f(1,1,0) |  |

|    | 10 | f(1,0,1) | f(1,0,0) |  |

|    |    | (        | 2        |

|----|----|----------|----------|

|    |    | 1        | 0        |

|    | 11 | f(1,1,1) | f(1,1,0) |

| ab | 01 | f(0,1,1) | f(0,1,0) |

| ab | 00 | f(0,0,1) | f(0,0,0) |

|    | 10 | f(1,0,1) | f(1,0,0) |

|     |   |          | ł        | oc       |          |

|-----|---|----------|----------|----------|----------|

|     |   | 01       | 00       | 11       | 10       |

| a   | 0 | f(0,0,1) | f(0,0,0) | f(0,1,1) | f(0,1,0) |

| _ a | 1 | f(1,0,1) | f(1,0,0) | f(1,1,1) | f(1,1,0) |

|       |   |          | b        | С        |          |

|-------|---|----------|----------|----------|----------|

|       |   | 10       | 00       | 11       | 01       |

| a     | 0 | f(0,1,0) | f(0,0,0) | f(0,1,1) | f(0,0,1) |

| а<br> | 1 | f(1,1,0) | f(1,0,0) | f(1,1,1) | f(1,0,1) |

неправильное заполнение

Для функции трех переменных карта Карно - это прямоугольник 2х4 или 4х2 клетки. При разметке большей из осей нужно четко придерживаться последнего - четвертого - правила разметки и следить за тем, чтобы соседними не оказались сочетания 00 и 11 либо 01 и 10, в которых одновременно меняются обе переменные.

# Таблица истинности и карта Карно для функции четырех переменных

| r |   |   |   |            |

|---|---|---|---|------------|

| a | b | c | d | f(a,b,c,d) |

| 0 | 0 | 0 | 0 | f(0,0,0,0) |

| 0 | 0 | 0 | 1 | f(0,0,0,1) |

| 0 | 0 | 1 | 0 | f(0,0,1,0) |

| 0 | 0 | 1 | 1 | f(0,0,1,1) |

| 0 | 1 | 0 | 0 | f(0,1,0,0) |

| 0 | 1 | 0 | 1 | f(0,1,0,1) |

| 0 | 1 | 1 | 0 | f(0,1,1,0) |

| 0 | 1 | 1 | 1 | f(0,1,1,1) |

| 1 | 0 | 0 | 0 | f(1,0,0,0) |

| 1 | 0 | 0 | 1 | f(1,0,0,1) |

| 1 | 0 | 1 | 0 | f(1,0,1,0) |

| 1 | 0 | 1 | 1 | f(1,0,1,1) |

| 1 | 1 | 0 | 0 | f(1,1,0,0) |

| 1 | 1 | 0 | 1 | f(1,1,0,1) |

| 1 | 1 | 1 | 0 | f(1,1,1,0) |

| 1 | 1 | 1 | 1 | f(1,1,1,1) |

|    | ,  |            | c          | d          |            |

|----|----|------------|------------|------------|------------|

|    |    | 11         | 01         | 00         | 10         |

|    | 00 | f(0,0,1,1) | f(0,0,0,1) | f(0,0,0,0) | f(0,0,1,0) |

| ab | 01 | f(0,1,1,1) | f(0,1,0,1) | f(0,1,0,0) | f(0,1,1,0) |

| au | 11 | f(1,1,1,1) | f(1,1,0,1) | f(1,1,0,0) | f(1,1,1,0) |

|    | 10 | f(1,0,1,1) | f(1,0,0,1) | f(1,0,0,0) | f(1,0,1,0) |

|    | •  |            | c          | d          |            |

|----|----|------------|------------|------------|------------|

|    |    | 11         | 01         | 00         | 10         |

|    | 00 | f(0,0,1,1) | f(0,0,0,1) | f(0,0,0,0) | f(0,0,1,0) |

| ab | 10 | f(1,0,1,1) | f(1,0,0,1) | f(1,0,0,0) | f(1,0,1,0) |

| au | 11 | f(1,1,1,1) | f(1,1,0,1) | f(1,1,0,0) | f(1,1,1,0) |

|    | 01 | f(0,1,1,1) | f(0,1,0,1) | f(0,1,0,0) | f(0,1,1,0) |

Таблица истинности и карта Карно дня функции четырех переменных

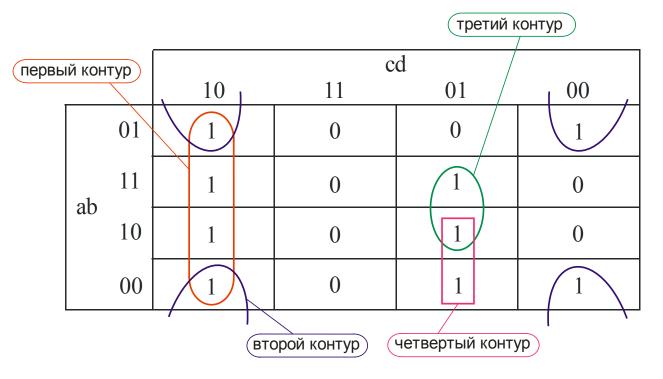

## Правила разметки контуров

Вместо значений функций в общем виде в клетки карты проставляются конкретные значения (логические 0 и 1) из соответствующих строк таблицы истинности. Затем рассматриваются только те клетки, которые заполнены единицами. Все эти единицы должны быть обведены контурами по следующим правилам составления контуров.

- **1.Контуры** должны быть прямоугольными и содержать количество единиц, равное 2n, где п целое число. Таким образом, в контуре может быть либо **одна**, либо **две**, либо **четыре**, либо **восемь единиц**.

- 2. Количество единиц в контуре должно быть максимальным, при этом контуры могут пересекаться между собой. Нужно учитывать, что крайние строки являются соседними и крайние столбцы также являются соседними, поэтому контуров разорванными. минимальное выражение как погическая сумма логических произведений. Каждому произведению 3. Количество контуров должно быть минимальным, но все единицы соответствует один контур карты Карно. В произведение входят только те должны быть охвачены контурами. Нельзя забывать об отдельно стоящих переменные, которые остаются в данном контуре неизменными. При этом единицах. Каждая такая единица это контур, которому соответствует переменная входит в произведение с инверсией, если ее значение в данном контуре равно 0, и без инверсии, если ее значение равно 1.

**Пример.** Написать максимальное и минимальное выражение для таблицы истинности, представленной ниже.

| a | b | c | f |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Максимальное выражение:

$$f = \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc}$$

Минимальное выражение:

$$f = b + a\overline{c}$$

# **Пример.** Написать максимальное и минимальное выражение для таблицы истинности, представленной ниже.

| a | b | c | d | f |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

Максимальное выражение:

$$f = \overline{abcd} + \overline{abcd} +$$

Минимальное выражение:

$$f = c\overline{d} + \overline{ad} + \overline{acd} + \overline{bcd}$$

### Базовые логические элементы

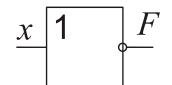

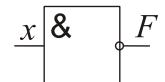

# 1. Инвертор $F = \overline{x}$

| X | F |

|---|---|

| 0 | 1 |

| 1 | 0 |

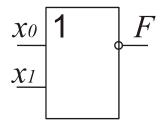

# 2. Логическое сложение (элемент ИЛИ) $F = x_0 \lor x_1$

$$\begin{array}{c|cccc} x_0 & 1 & F \\ \hline x_1 & & \end{array}$$

| $x_0$ | $x_1$ | F |

|-------|-------|---|

| 0     | 0     | 0 |

| 1     | 0     | 1 |

| 0     | 1     | 1 |

| 1     | 1     | 1 |

## 3. Логическое сложение с отрицанием (элемент ИЛИ-НЕ)

| $x_0$ | $x_1$ | F |

|-------|-------|---|

| 0     | 0     | 1 |

| 1     | 0     | 0 |

| 0     | 1     | 0 |

| 1     | 1     | 0 |

$$F = \overline{x_0 + x_1}$$

# 4. Логическое умножение (элемент И) $F = x_0 \wedge x_1$

$$x_0$$

&  $F$

| $x_0$ | $x_1$ | F |

|-------|-------|---|

| 0     | 0     | 0 |

| 1     | 0     | 0 |

| 0     | 1     | 0 |

| 1     | 1     | 1 |

$$F = x_0 \wedge x_1$$

## 5. Логическое умножение с отрицанием (элемент И-НЕ)

| $x_0$ | $x_1$ | F |

|-------|-------|---|

| 0     | 0     | 1 |

| 1     | 0     | 1 |

| 0     | 1     | 1 |

| 1     | 1     | 0 |

$$F = \overline{x_0 \cdot x_1}$$

# 6. Функция неравнозначности XOR (исключающее ИЛИ)

$$x_0 = 1$$

$x_1$

$x_1$

| $x_0$ | $x_1$ | F |

|-------|-------|---|

| 0     | 0     | 0 |

| 1     | 0     | 1 |

| 0     | 1     | 1 |

| 1     | 1     | 0 |

$$F = x_0 \oplus x_1$$

# 7. Функция равнозначности (исключающее ИЛИ с инверсией)

$$x_0 = 1$$

$x_1$

| $x_0$ | $x_1$ | F |

|-------|-------|---|

| 0     | 0     | 1 |

| 1     | 0     | 0 |

| 0     | 1     | 0 |

| 1     | 1     | 1 |

$$F = \overline{x_0 \oplus x_1}$$

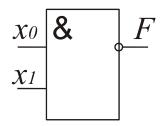

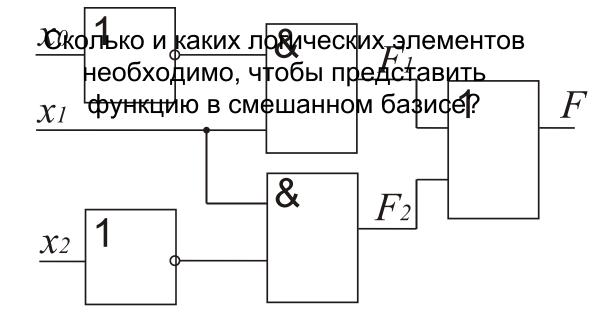

### Синтез логических схем

Смешанным базисом называется форма представления БФ (и/или набор логических элементов), в которой присутствуют, как операторы логического умножения, так и операторы логического сложения.

Пример.

$$F = x_2 x_1 x_0 + x_2 x_1 x_0 + x_2 x_1 x_0 = x_1 x_0 + x_2 x_1$$

Требуемые элементы:

- 2 инвертора,

- 2 элемента 2И

- 1 элемент 2ИЛИ

Функция представлена в *базисе И-НЕ*, если реализация функции содержит только элементы И-НЕ (логическое умножение с инверсией).

$F = (x_1 \overline{x_0}) \cdot (\overline{x_2} x_1)$

*Требуемые элементы:* 5 элементов 2И-НЕ

$$\frac{\overline{x_0} = \overline{x_0 \cdot x_0}}{\overline{x_2} = \overline{x_2 \cdot x_2}}$$

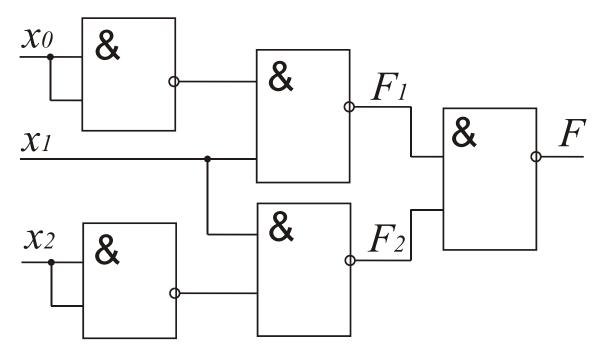

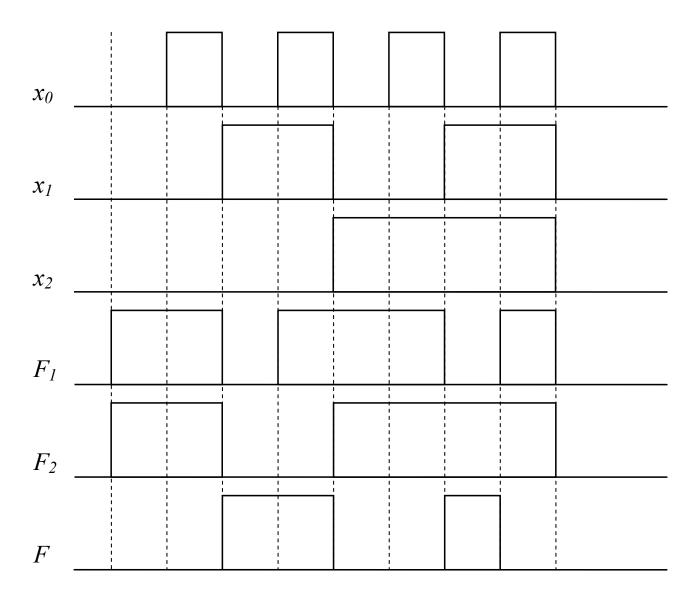

# Диаграммы работы схемы:

$$F = (\overline{x_1} \overline{x_0}) \cdot (\overline{x_2} x_1)$$

Функция представлена в базисе ИЛИ-НЕ, если реализация функции содержит только элементы ИЛИ-НЕ (логическое сложение с инверсией).

**Пример.** Функция  $F = x_2 x_1 x_0 + x_2 x_1 x_0 + x_2 x_1 x_0 = x_1 x_0 + x_2 x_1$

с использованием теоремы Де-Моргана может быть

представлена в следующем виде:

$$F = (\overline{x_1} + x_0) + (x_2 + \overline{x_1})$$

Требуемые элементы:

3 элемента 2ИЛИ-НЕ

1 элемент 2ИЛИ

$u\pi u$

5 элементов 2ИЛИ-НЕ

$$\overline{F} = F$$

32

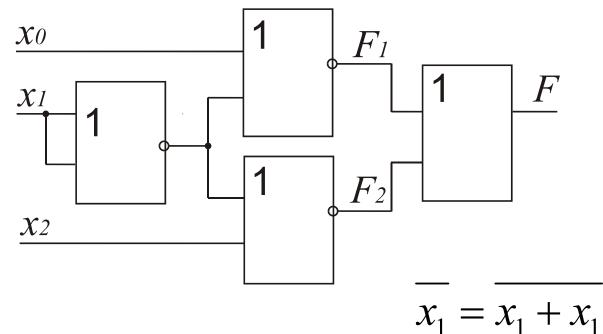

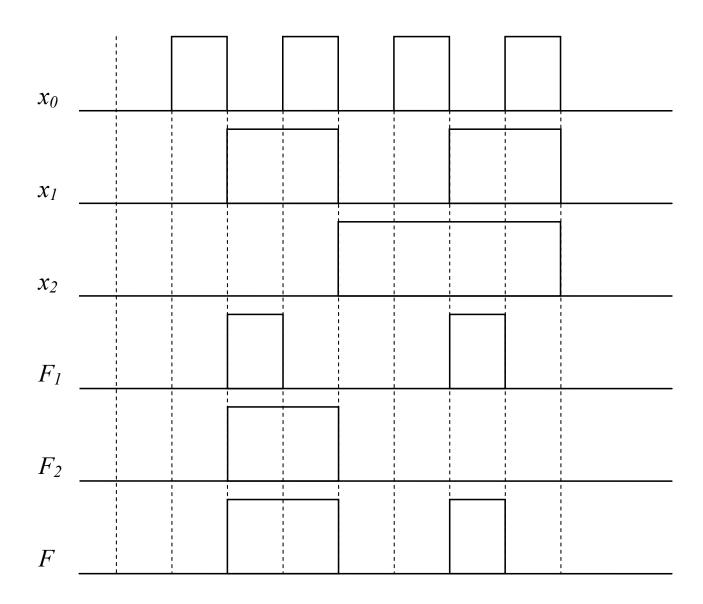

# Диаграммы работы схемы:

$$F = (\overline{\overline{x_1} + x_0}) + (\overline{x_2 + \overline{x_1}})$$

## Семейства логических элементов

**Корпуса интегральных микросхем цифровых устройств,** как правило, имеют 14 или 16 ножек.

| Тип микросхемы | 14 ножек | 16 ножек |

|----------------|----------|----------|

| питание        | 14       | 16       |

| земля          | 7        | 8        |

# Два основных типа построения логических схем:

- 1. ТТЛ-схемы и ТТЛШ-схемы,

- 2. КМОП-схемы.

### Семейство ТТЛ-схем

ТТЛ-схемы построены на основе **транзисторно-транзисторной** логики. ТТЛШ-схемы отличаются от ТТЛ-схем применением диодов и транзисторов Шоттки. Это позволяет в несколько раз сократить времена переключения схем.

#### Все ТТЛ-схемы имеют следующие общие характеристики:

- напряжение питания +5 В;

- все они имеют совместимые входные и выходные сигналы, поэтому возможно произвольное соединение элементов друг с другом;

- совместимость по выводам элементов одного названия, но разных серий.

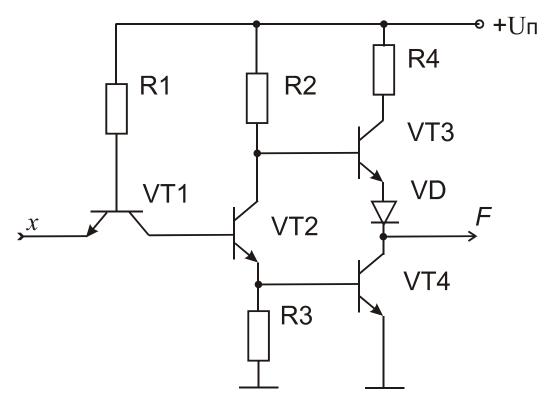

## ТТЛ-инвертор

Структура выходного каскада, состоящая из транзисторов *VT3,VT4* и диода *VD*, называется *двухтактным выходным каскадом*. Такие каскады не могут быть включены параллельно, т.е. ТТЛ-элементы с двухтактным выходным каскадом *не могут объединяться по выходу*.

Если x = 0, то VT1 открыт,  $UK\Theta_{VT1} \sim 0 = UE\Theta_{VT2}$ , To VT2 закрыт, ток через него не течет, UR3 = $0 \rightarrow VT4$ закрыт. UK $\Theta_{VT2} \sim U \Pi =$ UБЭ $_{VT3}$  → VT3 открыт. →  $F \sim \text{Uп}$  или равно "1". Если x = 1, то VT1 закрыт,  $IK0_{VT1}$  открывает VT2, напряжение на его коллекторе уменьшается, VT3 закрывается. Протекающий через VT2 ток создает падение на R3. → VT4 открывается.  $\rightarrow F = 0$ .

# ТТЛ-элемент 2И-НЕ

При подключении одного из эмиттеров I1 или I2 к «0» транзистор VT1 открывается, и приводит к закрытию транзисторов VT2 и VT4. База транзистора VT3 через резистор R2 соединена с положительным полюсом источника питания. Следовательно, он находится в открытом состоянии, и на выход схемы F через резистор R4 диод VD подается напряжение высокого уровня. Резистор R3 (150...500 Ом) служит для ограничения тока.

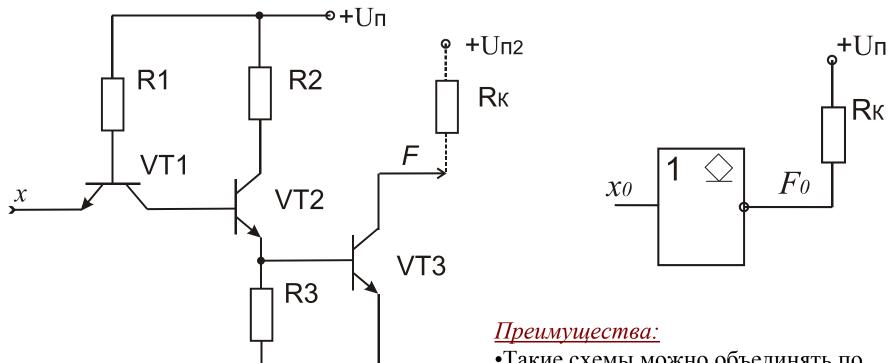

# Элементы с открытым коллектором

Инвертор с открытым коллектором

Внешний резистор  $R_K$  обязателен.

- •Такие схемы можно объединять по выходу

- •На нагрузку может подаваться напряжение, превышающее напряжение питания. Ограничением является максимально допустимое напряжение пробоя выходного транзистора.

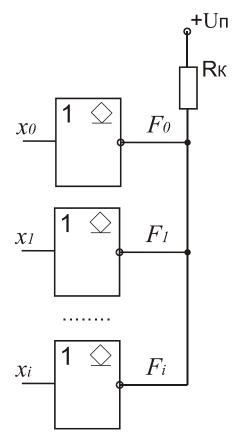

#### Монтажное ИЛИ

| F | = | $\chi_2$ | $\cdot \chi_{_{1}}$ | $\cdot \chi_{0}$ |

|---|---|----------|---------------------|------------------|

|   |   |          | 1                   | U                |

| $x_2$ | $x_{I}$ | $x_0$ | F |

|-------|---------|-------|---|

| 0     | 0       | 0     | 1 |

| 0     | 0       | 1     | 0 |

| 0     | 1       | 0     | 0 |

| 0     | 1       | 1     | 0 |

| 1     | 0       | 0     | 0 |

| 1     | 0       | 1     | 0 |

| 1     | 1       | 0     | 0 |

| 1     | 1       | 1     | 0 |

Схема монтажного ИЛИ получается при соединении нескольких выходов с открытым коллектором. Для получения низкого уровня напряжения на общем выводе достаточно, чтобы *один* из выходных транзисторов был открыт.

Принцип «монтажное ИЛИ» позволяет реализовать общую шину, для чего несколько выходов логических элементов с открытыми коллекторами соединяются вместе. Для обеспечения требуемого уровня напряжения на шине необходимо корректно выбирать величину нагрузочного резистора  $R_{K}$ .

#### $\underline{P}$ екомендации по выбору $\underline{R}_K$ :

- 1. При высоком уровне напряжения через резистор  $R_K$  текут токи выходных транзисторов  $I_{FH}$  и входные токи  $I_{IH}$ . Величина этого резистора должна быть достаточно маленькой, чтобы уровень выходного напряжения не упал ниже допустимого высокого уровня входного напряжения последующей схемы

- 2. При низком уровне напряжения в худшем случае работает только один транзистор. Величина резистора  $R_K$  должна быть достаточно большой, чтобы ток коллектора не достиг значения  $I_{0Lmax}$ . Также необходимо помнить, что через резистор протекают входные токи  $I_{\rm IL}$  подключенных схем.

$$R_{\text{max}} = \frac{U_{II} - 2.7B}{K \cdot I_{EH} + N \cdot I_{IH}}$$

$$R_{\min} = \frac{U_{II} - 0.4B}{I_{OL\max} - N \cdot \left| I_{IL} \right|}$$

K – количество параллельно соединенных выводов,

N – количество параллельно соединенных входов последующей схемы

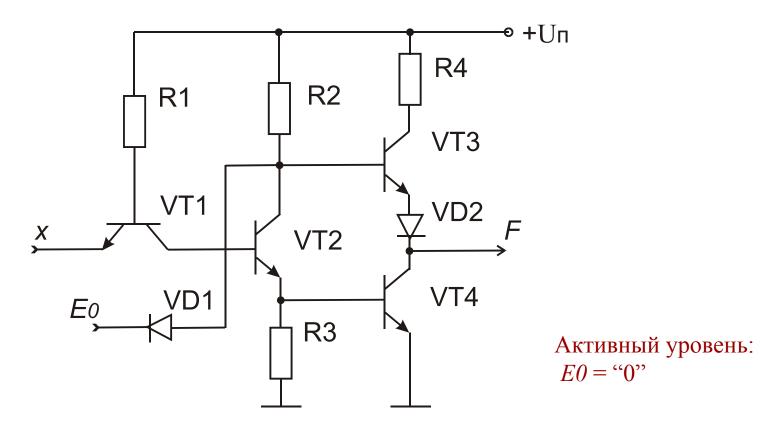

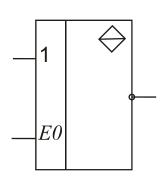

# ТТЛ - инвертор с Z-состоянием (3-м состоянием)

Если E0 = "1", VD1 не проводит и не оказывает влияния на работу инвертора.

Если E0 = "0", VD1 проводит,  $U_{K \ni VT2} = 0$ ,  $U_{B \ni VT3} = 0 \rightarrow VT2$  и VT3 закрыты, через VT2 ток не течет, то  $U_{R3} = 0 \rightarrow VT4$  тоже закрыт.

Таким образом, выход F отключен и от питания, и от земли, т.е. находится в Z-состоянии.

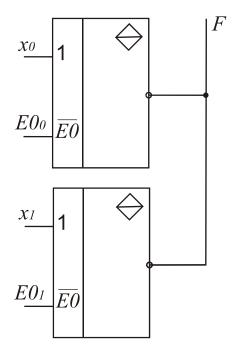

# Элементы с Z-состоянием также позволяют реализовать общую шину

Активный уровень E0 = "0"

- Такие элементы можно объединять по выходу.

- Одновременная работа 2-х и более элементов запрещена.

- Схемы с Z-состоянием используются в системах с общей шиной. Три выходных состояния обычно обозначают как H, L и Z.

# Основные параметры микросхем серии ТТЛ

| серия | $U_{\text{BX}}^{0}$ , | $U_{\text{BX}}^{-1}$ , | $I_{\text{BX}}^{0}$ , | $I_{\text{BX}}^{-1}$ , | $U_{\text{вых}}^{0}$ , | $U_{\text{вых}}^{-1}$ , | $I_{\text{вых}}^{0}$ , | $I_{\text{вых}}^{1}$ , | $f_{\text{max}}$ , | $I_{\text{потр}}$ , | С <sub>н</sub> , | $C_{\text{вых}}$ | $C_{BX}$ , |

|-------|-----------------------|------------------------|-----------------------|------------------------|------------------------|-------------------------|------------------------|------------------------|--------------------|---------------------|------------------|------------------|------------|

|       | В                     | В                      | мА                    | мА                     | В                      | В                       | мА                     | мА                     | МΓц                | мА                  | пΦ               | пΦ               | пΦ         |

| 155   | ≤ 0,4                 | ≥ 2,4                  | 1,6                   | 0,04                   | ≤ 0,4                  | ≥ 2,4                   | 16                     | 0,4                    | 10                 | ~15                 | 100              | 15               | 10         |

| 1533  | ≤ 0,4                 | ≥ 2,7                  | 0,16                  | 0,004                  | ≤ 0,4                  | ≥ 2,7                   | 1,6                    | 0,04                   | 50                 | ~1,5                | 60               | 10               | 8          |

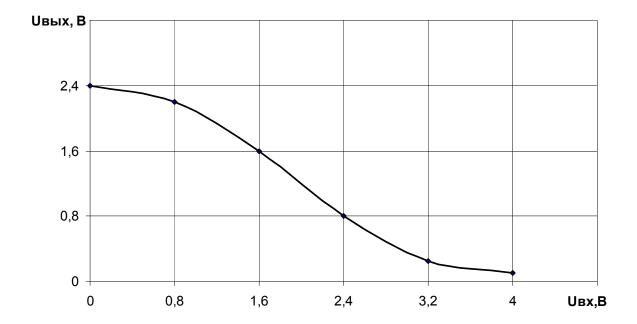

#### Передаточная характеристика инвертора серии ТТЛ

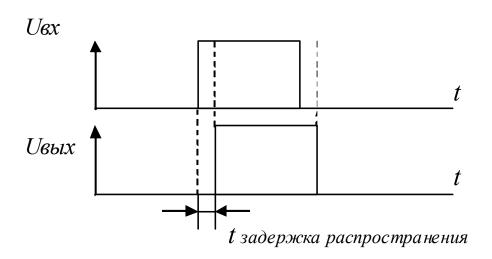

# Задержка распространения сигнала

| Серия         |            | Параметр  | Нагрузка             |           |        |                      |

|---------------|------------|-----------|----------------------|-----------|--------|----------------------|

| Отечественная | Зарубежная | Рпот, мВт | t <sub>зд</sub> , нс | Епот, пДж | Сн, пФ | R <sub>H</sub> , кОм |

| K134          | 74L        | 1         | 33                   | 33        | 50     | 4                    |

| K155          | 74         | 10        | 9                    | 90        | 15     | 0,4                  |

| K131          | 74H        | 22        | 6                    | 132       | 25     | 0,28                 |

| K555          | 74LS       | 2         | 9,5                  | 19        | 15     | 2                    |

| K531          | 74S        | 19        | 3                    | 57        | 15     | 0,28                 |

| K1533         | 74ALS      | 1,2       | 4                    | 4,8       | 15     | 2                    |

| K1531         | 74F        | 4         | 3                    | 12        | 15     | 0,28                 |

# Правила эксплуатации микросхем серий ТТЛ

- 1. Входы микросхем можно оставлять свободными, в этом случае на входе имеем логическую единицу. Но, при этом снижается помехоустойчивость ИМС.

- 2. Для получения логической единицы на входе, входы соединяются с источником питания через резистор R= 1 кОм. На один резистор можно подключать до 20 входов. Чтобы получить логический ноль, вход заземляется.

- 3. Запрещается соединять выходы между собой (за исключением элементов с открытым коллектором или с Z-состоянием).

- 4. Для исключения импульсных помех по цепям питания рекомендуется ставить керамические (безиндуктивные) конденсаторы 0,1 мкФ на каждые 3 корпуса ИМС.

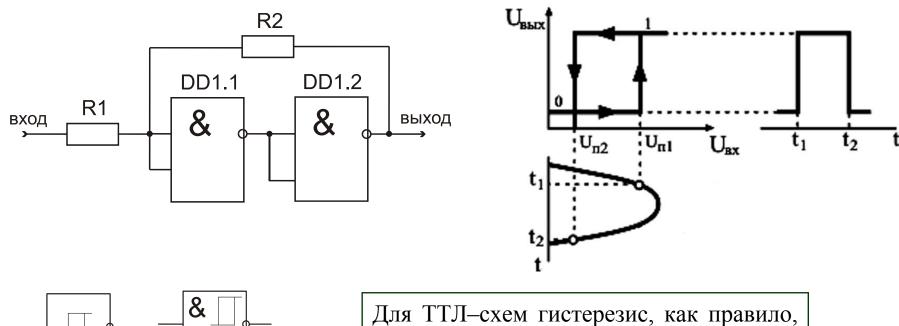

# Использование триггера Шмитта во входных цепях логических элементов

**Триггер Шмитта** - это специфический вид триггера, имеющего один вход и один выход. В устройствах с триггером Шмитта переход из одного устойчивого состояния в другое осуществляется при определенных уровнях входного напряжения, называемых **пороговыми уровнями**.

составляет 0.8 В, для КМОП–элементов он зависит от напряжения питания и определяется как  $U\Gamma = 0.27*U\Pi-0.55B$ .

#### Применение триггеров Шмитта:

- ❖ Использование триггера Шмитта во входных цепях позволяет сократить время переключения элемента.

- **❖** Для преобразования аналоговых колебаний в прямоугольные импульсы, которые затем уже используются в цифровой технике.

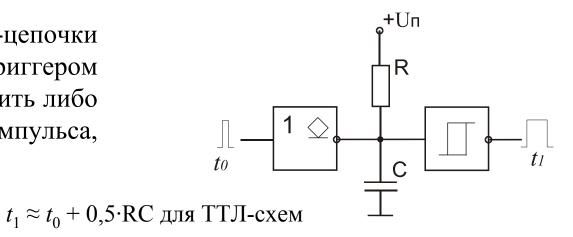

- ❖ При объединении RC-цепочки и элемента с триггером Шмитта можно получить либо схему расширения импульса, либо генератор.

❖ Триггеры Шмитта целесообразно также использовать в цепях установки начального состояния цифровых устройств в тех случаях, когда постоянная времени установления выходного напряжения источника питания велика и необходимо обеспечить большую длительность импульса сброса и его крутой спад.

#### Семейство КМОП

(комплементарная пара транзисторов на основе п/п структуры металл-оксид-полупроводник)

#### Основные особенности элементов КМОП:

- Напряжение питания +5...15В (3...18В);

- Очень низкие входные токи;

- В стационарном режиме и на низких частотах очень низкая мощность рассеяния;

- И при низком, и при высоком уровне напряжений выходные токи достаточно большие

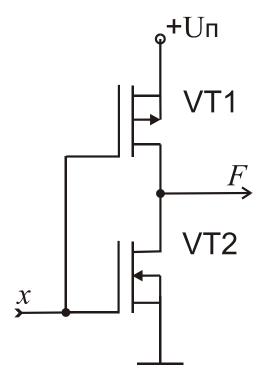

# Инвертор

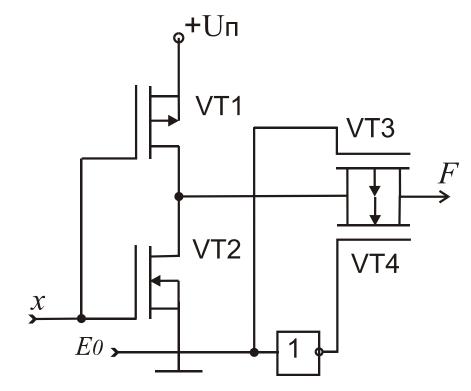

# Инвертор с Z-состоянием

Если x = "0", VT1 - открыт, VT2 - закрыт. И наоборот.

Если E0 = "1", то "1" на затворе VT3 и "0" на затворе VT4  $\rightarrow$  они оба закрыты, выход отключен и от питания, и от земли, т.е. в Z-состоянии. Если E0 = "0", то VT3 и VT4 открыты, оба открытых транзистора не оказывают влияния на работу инвертора.

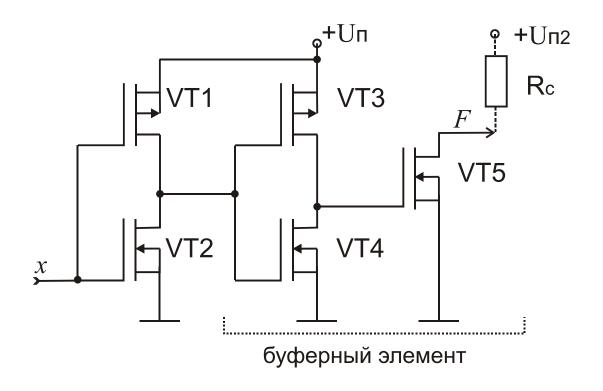

## Инвертор с открытым стоком

Если x = "0", VT1 - открыт, VT2 - закрыт. На затворах VT3 и VT4 "1"  $\rightarrow VT3 -$  закрыт, VT4 - открыт. На затворе VT5 "0", выход F подтянут  $\kappa$  +Uп через Rc.

Если x = "1", VT1 - закрыт, VT2 - открыт. На затворах VT3 и  $VT4 "0" \rightarrow VT3 - открыт$ , VT4 - закрыт. На затворе VT5 "1", выход F подключен к земле.

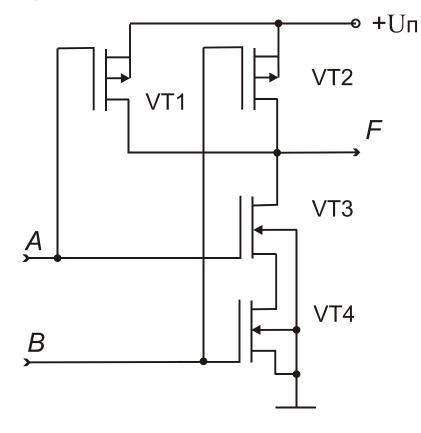

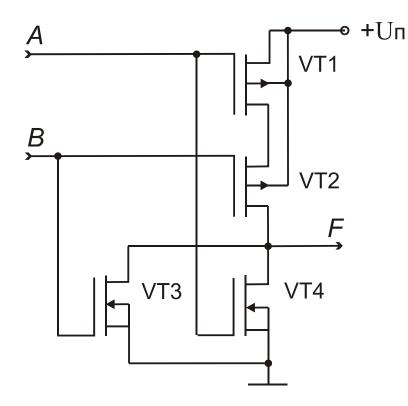

### КМОП-элемент 2И-НЕ

| A | В | $F = \overline{AB}$ |

|---|---|---------------------|

| 0 | 0 | 1                   |

| 1 | 0 | 1                   |

| 0 | 1 | 1                   |

| 1 | 1 | 0                   |

Когда на входе А и входе В логическая *единица*, транзисторы VT1 и VT2 закроются и на выходе *F* будет логический *ноль*. Если хотя бы на одном или на обоих входах будет логический *ноль*, то хотя бы один из нижних транзисторов закроется, один из верхних откроется, при этом на выходе будет логическая *единица*.

## КМОП-элемент 2ИЛИ-НЕ

| A | В | $F = \overline{A + B}$ |

|---|---|------------------------|

| 0 | 0 | 1                      |

| 1 | 0 | 0                      |

| 0 | 1 | 0                      |

| 1 | 1 | 0                      |

Если на входах *А* или *В* (или на обоих) логическая *единица*, то откроется один или оба из нижних транзисторов VT3, VT4, при этом закроется один или оба верхних транзистора, тогда на выходе логический *ноль*. Если на обоих входах логический *ноль*, то закроются оба нижних и откроются оба верхних транзистора, при этом на выходе логическая *единица*.

# Параметры логических элементов серий КМОП

| серия | U <sub>n</sub> , | $U_{\text{BX}}^{0}$ , | $U_{\text{BX}}^{-1}$ , | $U_{\text{вых}}^{0}$ , | $U_{\text{вых}}^{-1}$ , | $I_{\text{вых}}$ , | $I_{\text{потр}}$ , | С <sub>н</sub> , | $f_{\max}$ , | t <sub>зад</sub> , |

|-------|------------------|-----------------------|------------------------|------------------------|-------------------------|--------------------|---------------------|------------------|--------------|--------------------|

|       | В                | В                     | В                      | В                      | В                       | мкА                | мА                  | пΦ               | МГц          | нс                 |

| 561   | 3-15             | $\leq$ 0,3 $U_{\pi}$  | $\geq$ 0,8 $U_{\pi}$   | ≤0,1U <sub>π</sub>     | ≥0,9U <sub>п</sub>      | 10                 | 10                  | 40-50            | 1-5          | 50                 |

| 176   | 9                | 3                     | 8                      | ≤ 1                    | ≥ 8                     | 10                 | 10                  | 40-50            | 1            | 200                |

| 1554  | 5                | ≤ 0,4                 | ≥ 2,7                  | ≤ 0,1                  | ≥ 3,5                   | 40 мА              | 3 мА                | 30               | 120          | 10                 |

Передаточная характеристика такая же, как у ТТЛ. Различие в большем диапазоне напряжения питания.

# Особенности эксплуатации логических элементов КМОП:

- 1. Запрещается оставлять входы свободными, поэтому они подключаются к земле или к источнику питания (нагрузочное сопротивление не нужно);

- 2. Максимально допустимая C нагрузки на выход составляет ~100 пФ и не должна его превышать;

- 3. При монтаже логических элементов необходимо соединять шину питания и землю между собой. Если есть стабилитрон, то не нужно.

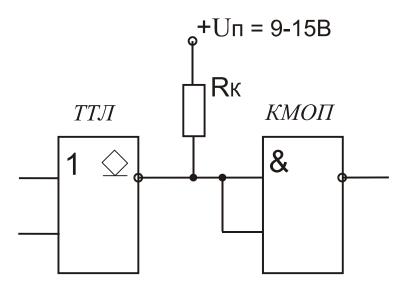

# Согласование уровней ТТЛ и КМОП

#### Появление ложных значений функций в реальных схемах

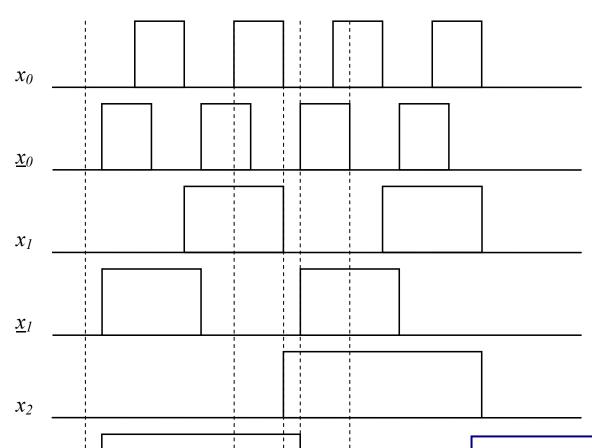

Выходной импульс появляется с задержкой, если мы имеем две или более ветви, которые содержат разное количество элементов. На выходе могут появиться ложные "0" или "1". Такое явление называют «гонками» или «состязаниями».

$\underline{x}_2$

Пример. Построить диаграммы для функции с учетом состязаний

$$F = x_2 \cdot \overline{x_1} \cdot \overline{x_0} + \overline{x_2} \cdot x_1 \cdot x_0$$

**Способ борьбы** – поставить в цепь, где меньше элементов (в данном случае в цепь  $x_0$  и  $x_1$  во второй сумме), элементы задержки (повторитель, два инвертора)

# Обозначение логических элементов

серия\_ функциональное назначение \_№

| Функц.<br>назначение | И  | ИЛИ | И-НЕ | ИЛИ-НЕ | HE |

|----------------------|----|-----|------|--------|----|

| Обозначение          | ЛИ | ЛЛ  | ЛА   | ЛЕ     | ЛН |